랜덤 액세스 메모리

컴퓨터에서 랜덤 액세스 메모리(영어: random-access memory, rapid access memory, 임의 접근 메모리 또는 임의 접근 기억 장치, 문화어: 자유기억기, 읽기쓰기기억기, 자유접근기억기[1] 순화어: 막기억장치) 즉 램(RAM)은 전자 컴퓨터 메모리의 한 형태로, 임의의 순서로 데이터를 읽고 변경할 수 있으며, 일반적으로 작업 데이터 및 기계어를 저장하는 데 사용된다.[2][3] 랜덤 액세스 메모리 장치는 하드 디스크 및 자기 테이프와 같이 데이터 항목의 읽기 또는 쓰기 시간이 기록 매체의 물리적 위치에 따라 회전 속도 및 암 이동과 같은 기계적 제한으로 인해 크게 달라지는 다른 직접 액세스 데이터 저장 매체와 대조적으로 메모리 내 데이터의 물리적 위치와 관계없이 거의 동일한 시간 내에 데이터 항목을 읽거나 쓸 수 있다.

오늘날의 기술에서 랜덤 액세스 메모리는 집적 회로(IC) 칩 형태로 MOS(금속-산화물-반도체) 메모리 셀을 사용한다. RAM은 일반적으로 전원이 제거되면 저장된 정보가 손실되는 휘발성 메모리 유형과 관련이 있다. 휘발성 랜덤 액세스 반도체 메모리의 두 가지 주요 유형은 정적 램(SRAM)과 동적 램(DRAM)이다.

비휘발성 RAM도 개발되었으며[4] 다른 유형의 비휘발성 메모리는 읽기 작업에 대해 랜덤 액세스를 허용하지만, 쓰기 작업을 허용하지 않거나 다른 종류의 제한이 있다. 여기에는 대부분의 ROM 및 NOR 플래시 메모리 유형이 포함된다.

반도체 RAM의 사용은 1965년 IBM이 System/360 Model 95 컴퓨터용 모놀리식(단일 칩) 16비트 SP95 SRAM 칩을 도입하고, 도시바가 180비트 Toscal BC-1411 전자 계산기에 양극성 DRAM 메모리 셀을 사용하면서 시작되었는데, 둘 다 접합형 트랜지스터를 기반으로 한다. 양극성 DRAM은 자기코어 메모리보다 더 빠른 속도를 제공했지만, 당시 지배적이던 자기 코어 메모리의 낮은 가격과 경쟁할 수 없었다.[5] 1966년, 로버트 H. 데나드 박사는 캐패시터당 단일 MOS 트랜지스터가 있는 현대적인 DRAM 아키텍처를 발명했다.[6] 최초의 상업용 DRAM IC 칩인 1K 인텔 1103은 1970년 10월에 출시되었다. SDRAM은 1992년 삼성 KM48SL2000 칩과 함께 다시 도입되었다.

역사

[편집]

초기 컴퓨터는 주요 메모리 기능에 전자계전기, 기계식 카운터[7] 또는 지연선 기억기를 사용했다. 초음파 지연선은 데이터를 기록된 순서대로만 재현할 수 있는 직렬 장치였다. 자기 드럼은 비교적 저렴한 비용으로 확장될 수 있었지만, 메모리 항목의 효율적인 검색을 위해서는 드럼의 물리적 레이아웃에 대한 지식이 필요하여 속도를 최적화해야 했다. 진공관으로, 나중에는 개별 트랜지스터로 만들어진 래치들은 하드웨어 레지스터와 같이 더 작고 빠른 메모리에 사용되었다. 이러한 레지스터는 상대적으로 크고 많은 양의 데이터를 사용하는 데 너무 비쌌으며, 일반적으로 수십 또는 수백 비트의 메모리만 제공될 수 있었다.

랜덤 액세스 메모리의 첫 번째 실용적인 형태는 윌리엄스관이었다. 이 메모리는 브라운관 표면에 전하를 띤 점으로 데이터를 저장했다. CRT의 전자빔이 튜브의 점을 어떤 순서로든 읽고 쓸 수 있었기 때문에 메모리는 랜덤 액세스였다. 윌리엄스관의 용량은 수백에서 약 천 비트였지만, 개별 진공관 래치를 사용하는 것보다 훨씬 작고 빠르며 전력 효율이 높았다. 영국 맨체스터 빅토리아 대학교에서 개발된 윌리엄스관은 1948년 6월 21일 처음으로 프로그램을 성공적으로 실행한 맨체스터 베이비 컴퓨터에서 최초의 전자적으로 저장된 프로그램이 구현된 매체였다.[8] 사실, 윌리엄스관 메모리가 베이비 컴퓨터를 위해 설계된 것이 아니라, 베이비 컴퓨터는 메모리의 신뢰성을 입증하기 위한 테스트베드였다.[9][10]

자기코어 메모리는 1947년에 발명되어 1970년대 중반까지 개발되었다. 이는 자화된 링 배열에 의존하는 널리 퍼진 랜덤 액세스 메모리 형태가 되었다. 각 링의 자화 방향을 변경함으로써 링당 1비트의 데이터를 저장할 수 있었다. 모든 링이 선택 및 읽기 또는 쓰기를 위한 주소 와이어 조합을 가지고 있었기 때문에 어떤 순서로든 모든 메모리 위치에 접근할 수 있었다. 자기 코어 메모리는 1970년대 초반 집적 회로(IC)의 반도체 메모리로 대체될 때까지 컴퓨터 메모리의 표준 형태였다.[11]

집적 고정 기억 장치(ROM) 회로가 개발되기 전에는 영구적(또는 읽기 전용) 랜덤 액세스 메모리가 종종 주소 디코더에 의해 구동되는 다이오드 매트릭스 또는 특수하게 감긴 코어로프 메모리 평면을 사용하여 구성되었다.

반도체 메모리는 1960년대 접합형 트랜지스터를 사용한 양극성 메모리와 함께 등장했다. 더 빠르기는 했지만, 자기 코어 메모리의 낮은 가격과 경쟁할 수 없었다.[12]

MOS RAM

[편집]1957년, 벨 연구소에서 프로시와 데릭은 최초의 실리콘 다이옥사이드 전계 효과 트랜지스터를 제조했는데, 이는 드레인과 소스가 표면에 인접한 최초의 트랜지스터였다.[13] 그 후 1960년, 한 팀이 벨 연구소에서 작동하는 MOSFET을 시연했다.[14][15] 이는 1964년 페어차일드 반도체의 존 슈미트가 금속-산화물-반도체(MOS) 메모리를 개발하는 데 이어졌다.[11][16] 더 빠른 속도 외에도 MOS 반도체 메모리는 자기 코어 메모리보다 저렴하고 전력 소비가 적었다.[11] 1968년 페어차일드의 페데리코 파진에 의한 실리콘 게이트 MOS 집적 회로(MOS IC) 기술 개발은 MOS 메모리 칩 생산을 가능하게 했다.[17] MOS 메모리는 1970년대 초에 지배적인 메모리 기술로서 자기 코어 메모리를 능가했다.[11]

집적 양극성 정적 램(SRAM)은 1963년 페어차일드 반도체의 로버트 H. 노먼이 발명했다.[18] 이어서 1964년 페어차일드의 존 슈미트가 MOS SRAM을 개발했다.[11] SRAM은 자기 코어 메모리의 대안이 되었지만, 각 비트 데이터에 대해 6개의 MOS 트랜지스터가 필요했다.[19] SRAM의 상업적 사용은 1965년 IBM이 System/360 Model 95용 SP95 메모리 칩을 도입하면서 시작되었다.[12]

동적 램(DRAM)은 4개 또는 6개 트랜지스터 래치 회로를 각 메모리 비트당 단일 트랜지스터로 교체하여 메모리 밀도를 크게 높이는 대신 휘발성을 가지게 되었다. 데이터는 각 트랜지스터의 작은 정전 용량에 저장되었고, 전하가 사라지기 전에 몇 밀리초마다 주기적으로 새로 고쳐야 했다.

1965년에 출시된 도시바의 Toscal BC-1411 전자 계산기는[20][21][22] 저마늄 양극성 트랜지스터와 축전기로 구성된 개별 메모리 셀에 180비트 데이터를 저장하는 일종의 축전기 양극성 DRAM을 사용했다.[21][22] 축전기는 이전에 애터너소프-베리 컴퓨터의 드럼, 윌리엄스관 및 셀렉트론 튜브와 같은 메모리 방식에도 사용되었다. 양극성 DRAM은 자기 코어 메모리보다 빠른 속도를 제공했지만, 당시 지배적이던 자기 코어 메모리의 낮은 가격과 경쟁할 수 없었다.[23]

1966년 로버트 데나드는 MOS 기술의 특성을 조사하던 중 축전기를 만들 수 있음을 발견했고, MOS 축전기에 전하를 저장하거나 저장하지 않는 것이 비트의 1과 0을 나타낼 수 있으며, MOS 트랜지스터가 축전기에 전하를 쓰는 것을 제어할 수 있음을 발견했다. 이는 그가 캐패시터당 단일 MOS 트랜지스터가 있는 현대 DRAM 아키텍처를 개발하게 된 계기가 되었다.[19] 1967년, 데나드는 MOS 기술을 기반으로 한 단일 트랜지스터 DRAM 메모리 셀에 대해 IBM에 특허를 출원했다.[19][24] 최초의 상업용 DRAM IC 칩은 인텔 1103으로, 8 µm MOS 공정으로 반도체 제조되었으며, 1kbit의 용량을 가지고 1970년에 출시되었다.[11][25]

가장 초기의 DRAM은 종종 CPU 클록과 동기화되었고 초기 마이크로프로세서와 함께 사용되었다. 1970년대 중반, DRAM은 비동기식 설계로 전환했지만, 1990년대에는 동기식 작동으로 돌아왔다.[26][27] 1992년 삼성은 16Mbit 용량의 KM48SL2000을 출시했다.[28][29] 최초의 상업용 더블 데이터 레이트 SDRAM은 1998년 6월에 출시된 삼성의 64Mbit DDR SDRAM이었다.[30] GDDR(그래픽 DDR)은 SGRAM(동기 그래픽 RAM)의 한 형태로, 1998년 삼성에서 16Mbit 메모리 칩으로 처음 출시되었다.[31]

유형

[편집]일반적으로 RAM이라는 용어는 솔리드 스테이트 메모리 장치를, 특히 대부분의 컴퓨터에서 주 메모리를 의미한다. 현대 RAM의 널리 사용되는 두 가지 형태는 정적 램(SRAM)과 동적 램(DRAM)이다. SRAM에서 데이터 비트는 메모리 셀의 상태를 사용하여 저장되며, 일반적으로 6개의 MOSFET를 사용한다. 이 형태의 RAM은 생산 비용이 더 많이 들지만, 일반적으로 DRAM보다 빠르고 정적 전력이 덜 필요하다. 현대 컴퓨터에서 SRAM은 종종 CPU 캐시 메모리로 사용된다. DRAM은 트랜지스터와 축전기 쌍(일반적으로 MOSFET와 MOS 캐패시터)[32]를 사용하여 데이터 비트를 저장하며, 이들이 함께 DRAM 셀을 구성한다. 축전기는 높은 또는 낮은 전하(각각 1 또는 0)를 유지하며, 트랜지스터는 칩의 제어 회로가 축전기의 전하 상태를 읽거나 변경할 수 있도록 하는 스위치 역할을 한다. 이 형태의 메모리는 정적 RAM보다 생산 비용이 저렴하므로 현대 컴퓨터에서 사용되는 컴퓨터 메모리의 주요 형태이다.

정적 RAM과 동적 RAM 모두 전원이 시스템에서 제거되면 상태가 손실되므로 휘발성으로 간주된다. 대조적으로, 고정 기억 장치(ROM)는 선택된 트랜지스터를 영구적으로 활성화하거나 비활성화하여 데이터를 저장하므로 메모리를 변경할 수 없다. ROM의 쓰기 가능한 변형(예: EEPROM 및 NOR 플래시)은 ROM과 RAM의 특성을 모두 공유하며, 전원 없이도 데이터가 유지되고 특별한 장비 없이도 업데이트될 수 있다.

ECC 메모리(SRAM 또는 DRAM일 수 있음)는 패리티 비트 또는 오류 정정 코드를 사용하여 저장된 데이터의 무작위 오류(메모리 오류)를 감지 및 수정하는 특수 회로를 포함한다.

메모리 셀

[편집]메모리 셀은 컴퓨터 메모리의 기본적인 구성 요소이다. 메모리 셀은 1비트의 이진 정보를 저장하는 전자 회로이며, 논리 1(고전압 레벨)을 저장하도록 설정되고 논리 0(저전압 레벨)을 저장하도록 재설정되어야 한다. 그 값은 설정/재설정 프로세스에 의해 변경될 때까지 유지/저장된다. 메모리 셀의 값은 읽기를 통해 액세스할 수 있다.

SRAM에서 메모리 셀은 플립플롭 회로의 한 유형이며, 일반적으로 FET를 사용하여 구현된다. 이는 SRAM이 접근되지 않을 때 매우 낮은 전력을 필요로 하지만, 비용이 많이 들고 저장 밀도가 낮다는 것을 의미한다.

두 번째 유형인 DRAM은 축전기를 중심으로 구성된다. 이 축전기를 충전하고 방전하는 것으로 셀에 "1" 또는 "0"을 저장할 수 있다. 그러나 이 축전기의 전하는 천천히 새어 나가므로 주기적으로 새로 고쳐야 한다. 이러한 새로 고침 프로세스로 인해 DRAM은 더 많은 전력을 사용하지만, SRAM에 비해 더 높은 저장 밀도와 낮은 단위 비용을 달성할 수 있다.

|

|

주소 지정

[편집]유용하기 위해서는 메모리 셀을 읽고 쓸 수 있어야 한다. RAM 장치 내에서는 메모리 셀을 선택하기 위해 멀티플렉싱 및 디멀티플렉싱 회로가 사용된다. 일반적으로 RAM 장치는 와 같은 일련의 주소 라인을 가지고 있으며, 이 라인에 적용될 수 있는 비트의 각 조합에 대해 일련의 메모리 셀이 활성화된다. 이러한 주소 지정 때문에 RAM 장치는 거의 항상 2의 거듭제곱인 메모리 용량을 가진다.

일반적으로 여러 메모리 셀이 동일한 주소를 공유한다. 예를 들어, 4비트 "폭" RAM 칩은 각 주소에 대해 4개의 메모리 셀을 가진다. 종종 메모리의 폭과 마이크로프로세서의 폭이 달라 32비트 마이크로프로세서의 경우 8개의 4비트 RAM 칩이 필요할 수 있다.

종종 장치에서 제공할 수 있는 것보다 더 많은 주소가 필요하다. 이 경우 장치 외부의 멀티플렉서가 액세스되는 올바른 장치를 활성화하는 데 사용된다. RAM은 종종 바이트 주소 지정이 가능하지만, 워드 주소 지정이 가능한 RAM을 만드는 것도 가능하다.[33][34]

메모리 계층 구조

[편집]RAM에서는 데이터를 읽고 덮어쓸 수 있다. 많은 컴퓨터 시스템에는 프로세서 레지스터, 다이 내 SRAM 캐시, 외부 캐시, 동적 램, 페이징 시스템, 하드 드라이브의 가상 메모리 또는 스왑 공간으로 구성된 메모리 계층 구조가 있다. 이러한 전체 메모리 풀은 다양한 하위 시스템이 RAM의 랜덤 액세스 개념을 위반하는 매우 다른 액세스 타임을 가질 수 있음에도 불구하고 많은 개발자들이 "RAM"이라고 부를 수 있다. DRAM과 같은 계층 수준 내에서도 구성 요소의 특정 행, 열, 뱅크, 랭크, 채널 또는 인터리브 구성에 따라 액세스 시간이 달라지지만, 회전 기억 매체나 테이프에 대한 액세스 시간이 달라지는 정도는 아니다. 메모리 계층 구조를 사용하는 전체 목표는 전체 메모리 시스템의 총 비용을 최소화하면서 가능한 가장 빠른 평균 액세스 시간을 얻는 것이다(일반적으로 메모리 계층 구조는 맨 위에 빠른 CPU 레지스터, 맨 아래에 느린 하드 드라이브를 두어 액세스 시간을 따른다).

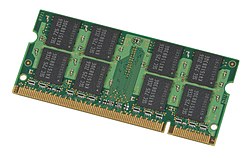

많은 최신 개인용 컴퓨터에서 RAM은 씹는 껌 몇 개 크기의 메모리 모듈 또는 DRAM 모듈이라는 쉽게 업그레이드할 수 있는 형태로 제공된다. 이는 손상되거나 변경되는 요구 사항에 따라 더 많은 저장 용량이 필요할 때 빠르게 교체할 수 있다. 위에서 언급했듯이 더 적은 양의 RAM(주로 SRAM)은 CPU 및 메인보드의 다른 IC뿐만 아니라 하드 드라이브, CD-ROM, 컴퓨터 시스템의 여러 다른 부분에도 통합되어 있다.

RAM의 다른 용도

[편집]

운영 체제 및 애플리케이션의 임시 저장 공간 및 작업 공간 역할을 하는 것 외에도 RAM은 다양한 다른 방식으로 사용된다.

가상 메모리

[편집]대부분의 최신 운영 체제는 "가상 메모리"라고 알려진 RAM 용량을 확장하는 방법을 사용한다. 컴퓨터의 하드 디스크 드라이브의 일부는 페이징 파일 또는 스크래치 파티션으로 할당되며, 물리적 RAM과 페이징 파일의 조합이 시스템의 총 메모리를 형성한다. (예를 들어, 컴퓨터에 2GB(10243B)의 RAM과 1GB의 페이지 파일이 있다면, 운영 체제는 총 3GB의 메모리를 사용할 수 있다.) 시스템의 물리적 메모리가 부족해지면, RAM의 일부를 페이징 파일로 "스왑"하여 새로운 데이터를 위한 공간을 만들거나 이전에 스왑된 정보를 다시 RAM으로 읽어올 수 있다. 이 메커니즘을 과도하게 사용하면 스레싱이 발생하여 전반적인 시스템 성능을 저해하는데, 이는 주로 하드 드라이브가 RAM보다 훨씬 느리기 때문이다.

램 드라이브

[편집]소프트웨어는 컴퓨터 RAM의 일부를 "파티션"하여 램 드라이브라고 불리는 훨씬 빠른 하드 드라이브처럼 작동하게 할 수 있다. 램 드라이브는 컴퓨터가 종료될 때 저장된 데이터를 잃어버리는데, 메모리가 대기 배터리 전원을 갖도록 배열되거나 램 드라이브의 변경 사항이 비휘발성 디스크에 기록되지 않는 한 그렇다. 램 드라이브는 램 드라이브 초기화 시 물리적 디스크에서 다시 로드된다.

섀도우 RAM

[편집]때로는 상대적으로 느린 ROM 칩의 내용을 읽기/쓰기 메모리로 복사하여 액세스 시간을 단축하기도 한다. 그러면 ROM 칩은 비활성화되고, 초기화된 메모리 위치는 동일한 주소 블록에(종종 쓰기 방지되어) 전환된다. 섀도잉이라고도 불리는 이 과정은 컴퓨터와 임베디드 시스템에서 흔히 볼 수 있다.

흔한 예로, 일반적인 개인용 컴퓨터의 바이오스에는 "use shadow BIOS"와 같은 옵션이 있다. 이 옵션을 활성화하면 BIOS ROM의 데이터에 의존하는 기능이 DRAM 위치를 대신 사용한다(대부분의 경우 비디오 카드 ROM 또는 다른 ROM 섹션의 섀도잉도 전환할 수 있다). 시스템에 따라 성능 향상으로 이어지지 않을 수 있으며 호환성 문제가 발생할 수도 있다. 예를 들어, 섀도우 RAM이 사용되면 일부 하드웨어는 운영체제에 액세스할 수 없을 수도 있다. 일부 시스템에서는 BIOS가 부팅 후 직접 하드웨어 액세스를 선호하여 사용되지 않기 때문에 이점은 가설에 불과할 수 있다. 사용 가능한 메모리는 섀도우된 ROM의 크기만큼 줄어든다.[35]

메모리 장벽

[편집]메모리 장벽은 CPU와 CPU 칩 외부 메모리의 응답 시간(이른바 메모리 지연 시간) 사이의 속도 격차가 커지는 현상을 말한다. 이러한 격차의 중요한 이유는 칩 경계를 넘는 제한된 통신 대역폭으로, 이는 대역폭 장벽이라고도 불린다. 1986년부터 2000년까지 CPU 속도는 연간 55%의 속도로 향상된 반면, 오프칩 메모리 응답 시간은 10%만 향상되었다. 이러한 추세로 인해 메모리 지연 시간이 컴퓨터 성능의 압도적인 병목이 될 것으로 예상되었다.[36]

격차가 발생하는 또 다른 이유는 1980년대 PC 혁명 시작 이후 메모리 크기가 엄청나게 증가했기 때문이다. 원래 PC에는 1 메비바이트 미만의 RAM이 포함되어 있었고, 이는 종종 1 CPU 클록 사이클의 응답 시간을 가졌으며, 이는 0 대기 상태를 필요로 함을 의미했다. 더 큰 메모리 유닛은 단순히 신호가 더 큰 회로를 가로지르는 데 더 오래 걸리기 때문에 동일한 유형의 더 작은 유닛보다 본질적으로 느리다. 많은 기비바이트의 메모리 유닛을 1 클록 사이클의 응답 시간으로 구성하는 것은 어렵거나 불가능하다. 오늘날의 CPU는 여전히 1 메비바이트의 0 대기 상태 캐시 메모리를 가지고 있지만, 칩 간 통신의 대역폭 제한으로 인해 CPU 코어와 동일한 칩에 존재한다. 또한 정적 RAM으로 구성되어야 하는데, 이는 더 큰 메모리에 사용되는 동적 RAM보다 훨씬 비싸다. 정적 RAM은 또한 훨씬 더 많은 전력을 소비한다.

CPU 속도 향상은 주요 물리적 장벽과 현재 CPU 설계가 어떤 의미에서 이미 메모리 장벽에 도달했기 때문에 상당히 둔화되었다. 인텔은 2005년 문서에서 이러한 원인을 요약했다.[37]

우선, 칩 기하학적 구조가 축소되고 클록 주파수가 증가함에 따라 트랜지스터의 누설 전류가 증가하여 과도한 전력 소비와 발열로 이어진다. 둘째, 클록 주파수 증가에 메모리 액세스 시간이 보조를 맞추지 못하기 때문에 더 높은 클록 속도의 이점이 부분적으로 메모리 지연에 의해 상쇄된다. 셋째, 특정 응용 프로그램의 경우, 프로세서가 빨라짐에 따라 전통적인 직렬 아키텍처는 효율성이 떨어지고 있으며(이른바 폰 노이만 병목 현상으로 인해), 주파수 증가가 가져올 수 있는 모든 이득을 더욱 저해한다. 또한, 고체 장치 내에서 인덕턴스를 생성하는 수단의 한계로 인해, 피처 크기가 줄어들면서 신호 전송의 저항-용량(RC) 지연이 증가하고 있으며, 이는 주파수 증가가 해결하지 못하는 추가적인 병목 현상을 야기한다.

신호 전송의 RC 지연은 "클록 속도 대 IPC: 전통적인 마이크로아키텍처의 종말"[38]에서도 언급되었는데, 이는 2000년에서 2014년 사이에 평균 연간 CPU 성능 향상이 최대 12.5%에 이를 것으로 예상했다.

또 다른 개념은 프로세서-메모리 성능 격차인데, 이는 2D 칩에서 더 멀리 떨어져 있는 논리 및 메모리 측면 사이의 거리를 줄이는 3차원 집적 회로로 해결할 수 있다.[39] 메모리 서브시스템 설계는 시간이 지남에 따라 넓어지는 이 격차에 초점을 맞춰야 한다.[40] 이 격차를 해소하는 주요 방법은 캐시를 사용하는 것이다. 캐시는 프로세서 근처에 최근 작업과 명령을 저장하는 소량의 고속 메모리로, 자주 호출되는 경우 해당 작업이나 명령의 실행 속도를 높인다. 넓어지는 격차에 대처하기 위해 여러 수준의 캐싱이 개발되었으며, 고속 현대 컴퓨터의 성능은 진화하는 캐싱 기술에 의존한다.[41] 프로세서 속도 증가와 메인 메모리 액세스 속도 지연 사이에는 최대 53%의 차이가 있을 수 있다.[42]

솔리드 스테이트 하드 드라이브는 2012년 SATA3를 통해 약 400Mbit/s에서 2024년 NVMe/PCIe를 통해 약 7GB/s로 계속해서 속도가 증가하여 RAM과 하드 디스크 속도 간의 격차를 좁히고 있지만, RAM은 여전히 한 자릿수 이상 빠르며, 단일 레인 DDR5 8000MHz는 128GB/s의 속도를 낼 수 있고, 최신 GDDR SDRAM은 훨씬 더 빠르다. 빠르고 저렴하며 비휘발성 솔리드 스테이트 드라이브는 이전에 RAM이 수행하던 일부 기능(예: 서버 팜에서 즉시 사용 가능한 특정 데이터 보관)을 대체했다. 1테라바이트의 SSD 스토리지는 200달러에 구입할 수 있지만, 1TB의 RAM은 수천 달러가 들 것이다.[43][44]

타임라인

[편집]SRAM

[편집]| 도입 날짜 | 칩 이름 | 용량 (비트) | 액세스 타임 | SRAM 유형 | 제조사 | 공정 | MOSFET | Ref |

|---|---|---|---|---|---|---|---|---|

| 1963년 3월 | 빈칸 | 1 | ? | 양극성 (셀) | 페어차일드 | 빈칸 | 빈칸 | [12] |

| 1965 | ? | 8 | ? | 양극성 | IBM | ? | 빈칸 | |

| SP95 | 16 | ? | 양극성 | IBM | ? | 빈칸 | [45] | |

| ? | 64 | ? | MOSFET | 페어차일드 | ? | PMOS | [46] | |

| 1966 | TMC3162 | 16 | ? | 양극성 (TTL) | Transitron | ? | 빈칸 | [11] |

| ? | ? | ? | MOSFET | NEC | ? | ? | [47] | |

| 1968 | ? | 64 | ? | MOSFET | 페어차일드 | ? | PMOS | [47] |

| 144 | ? | MOSFET | NEC | ? | NMOS | |||

| 512 | ? | MOSFET | IBM | ? | NMOS | [46] | ||

| 1969 | ? | 128 | ? | 양극성 | IBM | ? | 빈칸 | [12] |

| 1101 | 256 | 850 ns | MOSFET | 인텔 | 12,000 nm | PMOS | [48][49][50][51] | |

| 1972 | 2102 | 1kbit | ? | MOSFET | 인텔 | ? | NMOS | [48] |

| 1974 | 5101 | 1 kbit | 800 ns | MOSFET | 인텔 | ? | CMOS | [48][52] |

| 2102A | 1 kbit | 350 ns | MOSFET | 인텔 | ? | NMOS (디플리션) | [48][53] | |

| 1975 | 2114 | 4 kbit | 450 ns | MOSFET | 인텔 | ? | NMOS | [48][52] |

| 1976 | 2115 | 1 kbit | 70 ns | MOSFET | 인텔 | ? | NMOS (HMOS) | [48][49] |

| 2147 | 4 kbit | 55 ns | MOSFET | 인텔 | ? | NMOS (HMOS) | [48][54] | |

| 1977 | ? | 4 kbit | ? | MOSFET | 도시바 | ? | CMOS | [49] |

| 1978 | HM6147 | 4 kbit | 55 ns | MOSFET | 히타치 | 3,000 nm | CMOS (트윈웰) | [54] |

| TMS4016 | 16 kbit | ? | MOSFET | 텍사스 인스트루먼트 | ? | NMOS | [49] | |

| 1980 | ? | 16 kbit | ? | MOSFET | 히타치, 도시바 | ? | CMOS | [55] |

| 64 kbit | ? | MOSFET | 마쓰시타 | |||||

| 1981 | ? | 16 kbit | ? | MOSFET | 텍사스 인스트루먼트 | 2,500 nm | NMOS | [55] |

| 1981년 10월 | ? | 4 kbit | 18 ns | MOSFET | 마쓰시타, 도시바 | 2,000 nm | CMOS | [56] |

| 1982 | ? | 64 kbit | ? | MOSFET | 인텔 | 1,500 nm | NMOS (HMOS) | [55] |

| 1983년 2월 | ? | 64 kbit | 50 ns | MOSFET | 미쓰비시 | ? | CMOS | [57] |

| 1984 | ? | 256 kbit | ? | MOSFET | 도시바 | 1,200 nm | CMOS | [55][50] |

| 1987 | ? | 1 Mbit | ? | MOSFET | 소니, 히타치, 미쓰비시, 도시바 | ? | CMOS | [55] |

| 1987년 12월 | ? | 256 kbit | 10 ns | BiMOS | 텍사스 인스트루먼트 | 800 nm | BiCMOS | [58] |

| 1990 | ? | 4 Mbit | 15–23 ns | MOSFET | NEC, 도시바, 히타치, 미쓰비시 | ? | CMOS | [55] |

| 1992 | ? | 16 Mbit | 12–15 ns | MOSFET | 후지쯔, NEC | 400 nm | ||

| 1994년 12월 | ? | 512 kbit | 2.5 ns | MOSFET | IBM | ? | CMOS (SOI) | [59] |

| 1995 | ? | 4 Mbit | 6 ns | 캐시 (SyncBurst) | 히타치 | 100 nm | CMOS | [60] |

| 256 Mbit | ? | MOSFET | 현대 | ? | CMOS | [61] |

DRAM

[편집]| 도입 날짜 | 칩 이름 | 용량 (비트) | DRAM 유형 | 제조사 | 공정 | MOSFET | 면적 | Ref |

|---|---|---|---|---|---|---|---|---|

| 1965 | 빈칸 | 1 bit | DRAM (셀) | 도시바 | 빈칸 | 빈칸 | 빈칸 | [21][22] |

| 1967 | 빈칸 | 1 bit | DRAM (셀) | IBM | 빈칸 | MOS | 빈칸 | [24][47] |

| 1968 | ? | 256 bit | DRAM (IC) | 페어차일드 | ? | PMOS | ? | [11] |

| 1969 | 빈칸 | 1 bit | DRAM (셀) | 인텔 | 빈칸 | PMOS | 빈칸 | [47] |

| 1970 | 1102 | 1kbit | DRAM (IC) | 인텔, 허니웰 | ? | PMOS | ? | [47] |

| 1103 | 1 kbit | DRAM | 인텔 | 8,000 nm | PMOS | 10 mm2 | [62][63][25] | |

| 1971 | μPD403 | 1 kbit | DRAM | NEC | ? | NMOS | ? | [64] |

| ? | 2 kbit | DRAM | General Instrument | ? | PMOS | 13 mm2 | [65] | |

| 1972 | 2107 | 4 kbit | DRAM | 인텔 | ? | NMOS | ? | [48][66] |

| 1973 | ? | 8 kbit | DRAM | IBM | ? | PMOS | 19 mm2 | [65] |

| 1975 | 2116 | 16 kbit | DRAM | 인텔 | ? | NMOS | ? | [67][11] |

| 1977 | ? | 64 kbit | DRAM | NTT | ? | NMOS | 35 mm2 | [65] |

| 1979 | MK4816 | 16 kbit | PSRAM | Mostek | ? | NMOS | ? | [68] |

| ? | 64 kbit | DRAM | 지멘스 | ? | VMOS | 25 mm2 | [65] | |

| 1980 | ? | 256 kbit | DRAM | NEC, NTT | 1,000–1,500 nm | NMOS | 34–42 mm2 | [65] |

| 1981 | ? | 288 kbit | DRAM | IBM | ? | MOS | 25 mm2 | [69] |

| 1983 | ? | 64 kbit | DRAM | 인텔 | 1,500 nm | CMOS | 20 mm2 | [65] |

| 256 kbit | DRAM | NTT | ? | CMOS | 31 mm2 | |||

| January 5, 1984 | ? | 8 Mbit | DRAM | 히타치 | ? | MOS | ? | [70][71] |

| February 1984 | ? | 1 Mbit | DRAM | 히타치, NEC | 1,000 nm | NMOS | 74–76 mm2 | [65][72] |

| NTT | 800 nm | CMOS | 53 mm2 | [65][72] | ||||

| 1984 | TMS4161 | 64 kbit | PSRAM (VRAM) | 텍사스 인스트루먼트 | ? | NMOS | ? | [73][74] |

| January 1985 | μPD41264 | 256 kbit | DPRAM (VRAM) | NEC | ? | NMOS | ? | [75][76] |

| June 1986 | ? | 1 Mbit | PSRAM | 도시바 | ? | CMOS | ? | [77] |

| 1986 | ? | 4 Mbit | DRAM | NEC | 800 nm | NMOS | 99 mm2 | [65] |

| 텍사스 인스트루먼트, 도시바 | 1,000 nm | CMOS | 100–137 mm2 | |||||

| 1987 | ? | 16 Mbit | DRAM | NTT | 700 nm | CMOS | 148 mm2 | [65] |

| October 1988 | ? | 512 kbit | HSDRAM | IBM | 1,000 nm | CMOS | 78 mm2 | [78] |

| 1991 | ? | 64 Mbit | DRAM | 마쓰시타, 미쓰비시, 후지쯔, 도시바 | 400 nm | CMOS | ? | [55] |

| 1993 | ? | 256 Mbit | DRAM | 히타치, NEC | 250 nm | CMOS | ? | |

| 1995 | ? | 4 Mbit | DPRAM (VRAM) | 히타치 | ? | CMOS | ? | [60] |

| January 9, 1995 | ? | 1 Gbit | DRAM | NEC | 250 nm | CMOS | ? | [79][60] |

| 히타치 | 160 nm | CMOS | ? | |||||

| 1996 | ? | 4 Mbit | FRAM | 삼성 | ? | NMOS | ? | [80] |

| 1997 | ? | 4 Gbit | QLC | NEC | 150 nm | CMOS | ? | [55] |

| 1998 | ? | 4 Gbit | DRAM | 현대 | ? | CMOS | ? | [61] |

| February 2001 | ? | 4 Gbit | DRAM | 삼성 | 100 nm | CMOS | ? | [55][81] |

| June 2001 | TC51W3216XB | 32 Mbit | PSRAM | 도시바 | ? | CMOS | ? | [82] |

SDRAM

[편집]| 도입 날짜 |

칩 이름 |

용량 (비트)[83] |

SDRAM 유형 |

제조업체 | 공정 | MOS- FET |

면적 (mm2) |

Ref |

|---|---|---|---|---|---|---|---|---|

| 1992 | KM48SL2000 | 16 Mbit | SDR | 삼성 | ? | CMOS | ? | [84][28] |

| 1996 | MSM5718C50 | 18 Mbit | RDRAM | 오키 | ? | CMOS | 325 | [85] |

| N64 RDRAM | 36 Mbit | RDRAM | NEC | ? | CMOS | ? | [86] | |

| ? | 1024 Mbit | SDR | 미쓰비시 | 150 nm | CMOS | ? | [55] | |

| 1997 | ? | 1024 Mbit | SDR | 현대전자 | ? | SOI | ? | [87] |

| 1998 | MD5764802 | 64 Mbit | RDRAM | 오키 | ? | CMOS | 325 | [85] |

| 1998년 3월 | Direct RDRAM | 72 Mbit | RDRAM | 램버스 | ? | CMOS | ? | [88] |

| 1998년 6월 | ? | 64 Mbit | DDR | 삼성 | ? | CMOS | ? | [89][90][91] |

| 1998 | ? | 64 Mbit | DDR | 현대 | ? | CMOS | ? | [87] |

| 128 Mbit | SDR | 삼성 | ? | CMOS | ? | [92][90] | ||

| 1999 | ? | 128 Mbit | DDR | 삼성 | ? | CMOS | ? | [90] |

| 1024 Mbit | DDR | 삼성 | 140 nm | CMOS | ? | [55] | ||

| 2000 | GS eDRAM | 32 Mbit | EDRAM | 소니, 도시바 | 180 nm | CMOS | 279 | [93] |

| 2001 | ? | 288 Mbit | RDRAM | 하이닉스 | ? | CMOS | ? | [94] |

| ? | DDR2 | 삼성 | 100 nm | CMOS | ? | [91][55] | ||

| 2002 | ? | 256 Mbit | SDR | 하이닉스 | ? | CMOS | ? | [94] |

| 2003 | EE+GS eDRAM | 32 Mbit | eDRAM | 소니, 도시바 | 90 nm | CMOS | 86 | [93] |

| ? | 72 Mbit | DDR3 | 삼성 | 90 nm | CMOS | ? | [95] | |

| 512 Mbit | DDR2 | 하이닉스 | ? | CMOS | ? | [94] | ||

| 엘피다 | 110 nm | CMOS | ? | [96] | ||||

| 1024 Mbit | DDR2 | 하이닉스 | ? | CMOS | ? | [94] | ||

| 2004 | ? | 2048 Mbit | DDR2 | 삼성 | 80 nm | CMOS | ? | [97] |

| 2005 | EE+GS eDRAM | 32 Mbit | eDRAM | 소니, 도시바 | 65 nm | CMOS | 86 | [98] |

| 제노스 eDRAM | 80 Mbit | eDRAM | NEC | 90 nm | CMOS | ? | [99] | |

| ? | 512 Mbit | DDR3 | 삼성 | 80 nm | CMOS | ? | [91][100] | |

| 2006 | ? | 1024 Mbit | DDR2 | 하이닉스 | 60 nm | CMOS | ? | [94] |

| 2008 | ? | ? | LPDDR2 | 하이닉스 | ? | |||

| 2008년 4월 | ? | 8192 Mbit | DDR3 | 삼성 | 50 nm | CMOS | ? | [101] |

| 2008 | ? | 16384 Mbit | DDR3 | 삼성 | 50 nm | CMOS | ? | |

| 2009 | ? | ? | DDR3 | 하이닉스 | 44 nm | CMOS | ? | [94] |

| 2048 Mbit | DDR3 | 하이닉스 | 40 nm | |||||

| 2011 | ? | 16384 Mbit | DDR3 | 하이닉스 | 40 nm | CMOS | ? | [102] |

| 2048 Mbit | DDR4 | 하이닉스 | 30 nm | CMOS | ? | [102] | ||

| 2013 | ? | ? | LPDDR4 | 삼성 | 20 nm | CMOS | ? | [102] |

| 2014 | ? | 8192 Mbit | LPDDR4 | 삼성 | 20 nm | CMOS | ? | [103] |

| 2015 | ? | 12 Gbit | LPDDR4 | 삼성 | 20 nm | CMOS | ? | [92] |

| 2018 | ? | 8192 Mbit | LPDDR5 | 삼성 | 10 nm | FinFET | ? | [104] |

| 128 Gbit | DDR4 | 삼성 | 10 nm | FinFET | ? | [105] |

같이 보기

[편집]각주

[편집]- ↑ 0908남북한 공통 정보화교육 용어사전 나온다

- ↑ “RAM”. 《Cambridge English Dictionary》. 2019년 7월 11일에 확인함.

- ↑ “RAM”. 《Oxford Advanced Learner's Dictionary》. 2019년 7월 11일에 확인함.

- ↑ Gallagher, Sean (2013년 4월 4일). “Memory that never forgets: non-volatile DIMMs hit the market”. 《아르스 테크니카》. 2017년 7월 8일에 원본 문서에서 보존된 문서.

- ↑ “1966: Semiconductor RAMs Serve High-speed Storage Needs”. 《컴퓨터 역사 박물관》.

- ↑ US3387286A, Dennard, Robert H., "Field-effect transistor memory", issued 1968-06-04

- ↑ “IBM Archives -- FAQ's for Products and Services”. 《ibm.com》. 2012년 10월 23일에 원본 문서에서 보존된 문서.

- ↑ Napper, Brian, 《Computer 50: The University of Manchester Celebrates the Birth of the Modern Computer》, 2012년 5월 4일에 원본 문서에서 보존된 문서, 2012년 5월 26일에 확인함

- ↑ Williams, F. C.; Kilburn, T. (Sep 1948), “Electronic Digital Computers”, 《Nature》 162 (4117): 487, Bibcode:1948Natur.162..487W, doi:10.1038/162487a0, S2CID 4110351. Reprinted in The Origins of Digital Computers.

- ↑ Williams, F. C.; Kilburn, T.; Tootill, G. C. (Feb 1951), “Universal High-Speed Digital Computers: A Small-Scale Experimental Machine”, 《Proc. IEE》 98 (61): 13–28, doi:10.1049/pi-2.1951.0004, 2013년 11월 17일에 원본 문서에서 보존된 문서.

- ↑ 가 나 다 라 마 바 사 아 자 “1970: Semiconductors compete with magnetic cores”. 《컴퓨터 역사 박물관》. 2019년 6월 19일에 확인함.

- ↑ 가 나 다 라 “1966: Semiconductor RAMs Serve High-speed Storage Needs”. 《컴퓨터 역사 박물관》. 2019년 6월 19일에 확인함.

- ↑ Frosch, C. J.; Derick, L (1957). 《Surface Protection and Selective Masking during Diffusion in Silicon》. 《Journal of the Electrochemical Society》 (영어) 104. 547쪽. doi:10.1149/1.2428650.

- ↑ KAHNG, D. (1961). 《Silicon-Silicon Dioxide Surface Device》. 《Technical Memorandum of Bell Laboratories》. 583–596쪽. doi:10.1142/9789814503464_0076. ISBN 978-981-02-0209-5.

- ↑ Lojek, Bo (2007). 《History of Semiconductor Engineering》. Berlin, Heidelberg: Springer-Verlag Berlin Heidelberg. 321쪽. ISBN 978-3-540-34258-8.

- ↑ 《Solid State Design – Vol. 6》. Horizon House. 1965.

- ↑ “1968: Silicon Gate Technology Developed for ICs”. 《컴퓨터 역사 박물관》. 2019년 8월 10일에 확인함.

- ↑ US patent 3562721, Robert H. Norman, "Solid State Switching and Memory Apparatus", published 9 February 1971

- ↑ 가 나 다 “DRAM”. 《IBM100》. IBM. 2017년 8월 9일. 2019년 9월 20일에 확인함.

- ↑ Toscal BC-1411 calculator. 보관됨 2017-07-29 - 웨이백 머신, 과학박물관 (런던).

- ↑ 가 나 다 “Spec Sheet for Toshiba "TOSCAL" BC-1411”. 《Old Calculator Web Museum》. 2017년 7월 3일에 원본 문서에서 보존된 문서. 2018년 5월 8일에 확인함.

- ↑ 가 나 다 Toshiba "Toscal" BC-1411 Desktop Calculator 보관됨 2007-05-20 - 웨이백 머신

- ↑ “1966: Semiconductor RAMs Serve High-speed Storage Needs”. 《컴퓨터 역사 박물관》.

- ↑ 가 나 “Robert Dennard”. 《브리태니커 백과사전》. 2019년 7월 8일에 확인함.

- ↑ 가 나 Lojek, Bo (2007). 《History of Semiconductor Engineering》. Springer Science & Business Media. 362–363쪽. ISBN 9783540342588.

The i1103 was manufactured on a 6-mask silicon-gate P-MOS process with 8 μm minimum features. The resulting product had a 2,400 μm2 memory cell size, a die size just under 10 mm2, and sold for around $21.

- ↑ P. Darche (2020). 《Microprocessor: Prolegomenes - Calculation and Storage Functions - Calculation Models and Computer》. John Wiley & Sons. 59쪽. ISBN 9781786305633.

- ↑ B. Jacob; S. W. Ng; D. T. Wang (2008). 《Memory Systems: Cache, DRAM, Disk》. Morgan Kaufmann. 324쪽. ISBN 9780080553849.

- ↑ 가 나 《Electronic Design》. 《Electronic Design》 41 (Hayden Publishing Company). 1993.

The first commercial synchronous DRAM, the Samsung 16-Mbit KM48SL2000, employs a single-bank architecture that lets system designers easily transition from asynchronous to synchronous systems.

- ↑ “KM48SL2000-7 Datasheet”. Samsung. August 1992. 2019년 6월 19일에 확인함.

- ↑ “Samsung Electronics Develops First 128Mb SDRAM with DDR/SDR Manufacturing Option”. 《삼성전자》 (Samsung). 1999년 2월 10일. 2019년 6월 23일에 확인함.

- ↑ “Samsung Electronics Comes Out with Super-Fast 16M DDR SGRAMs”. 《삼성전자》 (Samsung). 1998년 9월 17일. 2019년 6월 23일에 확인함.

- ↑ Sze, Simon M. (2002). 《Semiconductor Devices: Physics and Technology》 (PDF) 2판. Wiley. 214쪽. ISBN 0-471-33372-7.

- ↑ 《The Essentials of Computer Organization and Architecture》. Jones & Bartlett Learning. 2006. ISBN 978-0-7637-3769-6.

- ↑ Anderson, Alexander John (2020년 10월 25일). 《Foundations of Computer Technology》. CRC Press. ISBN 978-1-000-15371-2.

- ↑ “Shadow Ram”. 2006년 10월 29일에 원본 문서에서 보존된 문서. 2007년 7월 24일에 확인함.

- ↑ 이 용어는 “Archived copy” (PDF). 2012년 4월 6일에 원본 문서 (PDF)에서 보존된 문서. 2011년 12월 14일에 확인함.에서 만들어졌다.

- ↑ “Platform 2015: Intel Processor and Platform Evolution for the Next Decade” (PDF). 2005년 3월 2일. 2011년 4월 27일에 원본 문서 (PDF)에서 보존된 문서.

- ↑ Agarwal, Vikas; Hrishikesh, M. S.; Keckler, Stephen W.; Burger, Doug (June 10–14, 2000). 〈Clock Rate versus IPC: The End of the Road for Conventional Microarchitectures〉 (PDF). 《Proceedings of the 27th Annual International Symposium on Computer Architecture》. 27th Annual International Symposium on Computer Architecture. Vancouver, BC. 2018년 7월 14일에 확인함.

- ↑ Rainer Waser (2012). 《Nanoelectronics and Information Technology》. John Wiley & Sons. 790쪽. ISBN 9783527409273. 2016년 8월 1일에 원본 문서에서 보존된 문서. 2014년 3월 31일에 확인함.

- ↑ Chris Jesshope and Colin Egan (2006). 《Advances in Computer Systems Architecture: 11th Asia-Pacific Conference, ACSAC 2006, Shanghai, China, September 6-8, 2006, Proceedings》. Springer. 109쪽. ISBN 9783540400561. 2016년 8월 1일에 원본 문서에서 보존된 문서. 2014년 3월 31일에 확인함.

- ↑ Ahmed Amine Jerraya and Wayne Wolf (2005). 《Multiprocessor Systems-on-chips》. Morgan Kaufmann. 90–91쪽. ISBN 9780123852519. 2016년 8월 1일에 원본 문서에서 보존된 문서. 2014년 3월 31일에 확인함.

- ↑ Celso C. Ribeiro and Simone L. Martins (2004). 《Experimental and Efficient Algorithms: Third International Workshop, WEA 2004, Angra Dos Reis, Brazil, May 25-28, 2004, Proceedings, Volume 3》. Springer. 529쪽. ISBN 9783540220671. 2016년 8월 1일에 원본 문서에서 보존된 문서. 2014년 3월 31일에 확인함.

- ↑ “SSD Prices Continue to Fall, Now Upgrade Your Hard Drive!”. 《MiniTool》 (미국 영어). 2018년 9월 3일. 2019년 3월 28일에 확인함.

- ↑ Coppock, Mark (2017년 1월 31일). “If you're buying or upgrading your PC, expect to pay more for RAM”. 《www.digitaltrends.com》. 2019년 3월 28일에 확인함.

- ↑ 《IBM first in IC memory》. IBM Corporation. 1965. 2019년 6월 19일에 확인함 – 컴퓨터 역사 박물관 경유.

- ↑ 가 나 Sah, Chih-Tang (October 1988). 《Evolution of the MOS transistor-from conception to VLSI》 (PDF). 《Proceedings of the IEEE》 76. 1280–1326 (1303)쪽. Bibcode:1988IEEEP..76.1280S. doi:10.1109/5.16328. ISSN 0018-9219.

- ↑ 가 나 다 라 마 “Late 1960s: Beginnings of MOS memory” (PDF). 《Semiconductor History Museum of Japan》. 2019년 1월 23일. 2019년 6월 27일에 확인함.

- ↑ 가 나 다 라 마 바 사 아 “A chronological list of Intel products. The products are sorted by date.” (PDF). 《Intel museum》. Intel Corporation. July 2005. 2007년 8월 9일에 원본 문서 (PDF)에서 보존된 문서. 2007년 7월 31일에 확인함.

- ↑ 가 나 다 라 “1970s: SRAM evolution” (PDF). 《Semiconductor History Museum of Japan》. 2019년 6월 27일에 확인함.

- ↑ 가 나 Pimbley, J. (2012). 《Advanced CMOS Process Technology》. Elsevier. 7쪽. ISBN 9780323156806.

- ↑ “Intel Memory”. 《Intel Vintage》. 2022년 3월 19일에 원본 문서에서 보존된 문서. 2019년 7월 6일에 확인함.

- ↑ 가 나 《Component Data Catalog》 (PDF). Intel. 1978. 3쪽. 2019년 6월 27일에 확인함.

- ↑ “Silicon Gate MOS 2102A”. Intel. 2019년 6월 27일에 확인함.

- ↑ 가 나 “1978: Double-well fast CMOS SRAM (Hitachi)” (PDF). 《Semiconductor History Museum of Japan》. 2019년 7월 5일에 확인함.

- ↑ 가 나 다 라 마 바 사 아 자 차 카 타 “Memory”. 《STOL (Semiconductor Technology Online)》. 2023년 11월 2일에 원본 문서에서 보존된 문서. 2019년 6월 25일에 확인함. 인용 오류: 잘못된

<ref>태그; "stol"이 다른 콘텐츠로 여러 번 정의되었습니다 - ↑ Isobe, Mitsuo; Uchida, Yukimasa; Maeguchi, Kenji; Mochizuki, T.; Kimura, M.; Hatano, H.; Mizutani, Y.; Tango, H. (October 1981). 《An 18 ns CMOS/SOS 4K static RAM》. 《IEEE Journal of Solid-State Circuits》 16. 460–465쪽. Bibcode:1981IJSSC..16..460I. doi:10.1109/JSSC.1981.1051623. S2CID 12992820.

- ↑ Yoshimoto, M.; Anami, K.; Shinohara, H.; Yoshihara, T.; Takagi, H.; Nagao, S.; Kayano, S.; Nakano, T. (1983). 〈A 64Kb full CMOS RAM with divided word line structure〉. 《1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers》 XXVI. 58–59쪽. doi:10.1109/ISSCC.1983.1156503. S2CID 34837669.

- ↑ Havemann, Robert H.; Eklund, R. E.; Tran, Hiep V.; Haken, R. A.; Scott, D. B.; P. K.; Ham, T. E.; Favreau, D. P.; Virkus, R. L. (December 1987). 〈An 0.8 μm 256K BiCMOS SRAM technology〉. 《1987 International Electron Devices Meeting》. 841–843쪽. doi:10.1109/IEDM.1987.191564. S2CID 40375699.

- ↑ Shahidi, Ghavam G.; Davari, Bijan; Dennard, Robert H.; Anderson, C. A.; Chappell, B. A.; 외. (December 1994). 《A room temperature 0.1 μm CMOS on SOI》. 《IEEE Transactions on Electron Devices》 41. 2405–2412쪽. Bibcode:1994ITED...41.2405S. doi:10.1109/16.337456. S2CID 108832941.

- ↑ 가 나 다 “Japanese Company Profiles” (PDF). Smithsonian Institution. 1996. 2019년 6월 27일에 확인함.

- ↑ 가 나 “History: 1990s”. 《SK하이닉스》. 2021년 2월 5일에 원본 문서에서 보존된 문서. 2019년 7월 6일에 확인함.

- ↑ “Intel: 35 Years of Innovation (1968–2003)” (PDF). Intel. 2003. 2019년 6월 26일에 확인함.

- ↑ The DRAM memory of Robert Dennard 보관됨 2020-08-01 - 웨이백 머신 history-computer.com

- ↑ “Manufacturers in Japan enter the DRAM market and integration densities are improved” (PDF). 《Semiconductor History Museum of Japan》. 2019년 6월 27일에 확인함.

- ↑ 가 나 다 라 마 바 사 아 자 차 Gealow, Jeffrey Carl (1990년 8월 10일). “Impact of Processing Technology on DRAM Sense Amplifier Design” (PDF). Massachusetts Institute of Technology. 149–166쪽. 2019년 6월 25일에 확인함 – CORE 경유.

- ↑ “Silicon Gate MOS 2107A”. Intel. 2019년 6월 27일에 확인함.

- ↑ “One of the Most Successful 16K Dynamic RAMs: The 4116”. 《국립 미국사 박물관》. Smithsonian Institution. 2023년 5월 31일에 원본 문서에서 보존된 문서. 2019년 6월 20일에 확인함.

- ↑ 《Memory Data Book And Designers Guide》 (PDF). Mostek. March 1979. 9 & 183쪽.

- ↑ “The Cutting Edge of IC Technology: The First 294,912-Bit (288K) Dynamic RAM”. 《국립 미국사 박물관》. Smithsonian Institution. 2019년 6월 20일에 확인함.

- ↑ “Computer History for 1984”. 《Computer Hope》. 2019년 6월 25일에 확인함.

- ↑ 《Japanese Technical Abstracts》. 《Japanese Technical Abstracts》 2 (University Microfilms). 1987. 161쪽.

The announcement of 1M DRAM in 1984 began the era of megabytes.

- ↑ 가 나 Robinson, Arthur L. (1984년 5월 11일). 《Experimental Memory Chips Reach 1 Megabit: As they become larger, memories become an increasingly important part of the integrated circuit business, technologically and economically》. 《Science》 224. 590–592쪽. doi:10.1126/science.224.4649.590. ISSN 0036-8075. PMID 17838349.

- ↑ 《MOS Memory Data Book》 (PDF). Texas Instruments. 1984. 4–15쪽. 2019년 6월 21일에 확인함.

- ↑ “Famous Graphics Chips: TI TMS34010 and VRAM”. 《IEEE 컴퓨터 학회》. 2019년 1월 10일. 2019년 6월 29일에 확인함.

- ↑ “μPD41264 256K Dual Port Graphics Buffer” (PDF). NEC 일렉트로닉스. 2019년 6월 21일에 확인함.

- ↑ “Sense amplifier circuit for switching plural inputs at low power”. 《구글 특허》. 2019년 6월 21일에 확인함.

- ↑ 《Fine CMOS techniques create 1M VSRAM》. 《Japanese Technical Abstracts》 2 (University Microfilms). 1987. 161쪽.

- ↑ Hanafi, Hussein I.; Lu, Nicky C. C.; Chao, H. H.; Hwang, Wei; Henkels, W. H.; Rajeevakumar, T. V.; Terman, L. M.; Franch, Robert L. (October 1988). 《A 20-ns 128-kbit*4 high speed DRAM with 330-Mbit/s data rate》. 《IEEE Journal of Solid-State Circuits》 23. 1140–1149쪽. Bibcode:1988IJSSC..23.1140L. doi:10.1109/4.5936.

- ↑ Breaking the gigabit barrier, DRAMs at ISSCC portend major system-design impact. (dynamic random access memory; International Solid-State Circuits Conference; Hitachi Ltd. and NEC Corp. research and development), January 9, 1995

- ↑ Scott, J.F. (2003). 〈Nano-Ferroelectrics〉. Tsakalakos, Thomas; Ovid'ko, Ilya A.; Vasudevan, Asuri K. 《Nanostructures: Synthesis, Functional Properties and Application》. Springer Science & Business Media. 584–600 (597)쪽. ISBN 9789400710191.

- ↑ “A Study of the DRAM industry” (PDF). MIT. 2010년 6월 8일. 2019년 6월 29일에 확인함.

- ↑ “Toshiba's new 32 Mb Pseudo-SRAM is no fake”. 《The Engineer》 (영어). 2001년 6월 24일. 2019년 6월 29일에 원본 문서에서 보존된 문서. 2019년 6월 29일에 확인함.

- ↑ Here, K, M, G, or T refer to the binary prefixes based on powers of 1024.

- ↑ “KM48SL2000-7 Datasheet”. 삼성. August 1992. 2019년 6월 19일에 확인함.

- ↑ 가 나 “MSM5718C50/MD5764802” (PDF). 오키 반도체. February 1999. 2019년 6월 21일에 원본 문서 (PDF)에서 보존된 문서. 2019년 6월 21일에 확인함.

- ↑ “Ultra 64 Tech Specs”. 《넥스트 제너레이션》. 14호 (Imagine Media). February 1996. 40쪽.

- ↑ 가 나 “역사: 1990년대”. 《az5miao》. 2022년 4월 4일에 확인함.

- ↑ “Direct RDRAM” (PDF). 램버스. 1998년 3월 12일. 2019년 6월 21일에 원본 문서 (PDF)에서 보존된 문서. 2019년 6월 21일에 확인함.

- ↑ “삼성전자, 초고속 16M DDR SGRAM 출시”. 《삼성전자》 (삼성). 1998년 9월 17일. 2019년 6월 23일에 확인함.

- ↑ 가 나 다 “삼성전자, DDR/SDR 제조 옵션으로 세계 최초 128Mb SDRAM 개발”. 《삼성전자》 (삼성). 1999년 2월 10일. 2019년 6월 23일에 확인함.

- ↑ 가 나 다 “삼성, 세계 최초 DDR3 메모리 프로토타입 시연”. 《Phys.org》 (미국 영어). 2005년 2월 17일. 2019년 6월 23일에 확인함.

- ↑ 가 나 “역사”. 《삼성전자》. 삼성. 2019년 6월 19일에 확인함.

- ↑ 가 나 “플레이스테이션 코어에 사용되는 EMOTION ENGINE과 GRAPHICS SYNTHESIZER가 하나의 칩으로 통합” (PDF). 소니. 2003년 4월 21일. 2017년 2월 27일에 원본 문서 (PDF)에서 보존된 문서. 2019년 6월 26일에 확인함.

- ↑ 가 나 다 라 마 바 “역사: 2000년대”. 《az5miao》. 2022년 4월 4일에 확인함.

- ↑ “삼성, 고성능 EDP 및 네트워크 애플리케이션용 업계 최고 속도 DDR3 SRAM 개발”. 《삼성 반도체》 (삼성). 2003년 1월 29일. 2019년 6월 25일에 확인함.

- ↑ “엘피다, 2GB DDR2 모듈 출하”. 《디 인콰이어러》. 2003년 11월 4일. 2019년 7월 10일에 원본 문서에서 보존된 문서. 2019년 6월 25일에 확인함.

- ↑ “삼성, 업계 최초 2기가비트 DDR2 SDRAM 선보여”. 《삼성 반도체》 (삼성). 2004년 9월 20일. 2019년 6월 25일에 확인함.

- ↑ “소니, 65nm 지원 반도체 설비 도입. 3년간 2,000억엔 투자”. 《pc.watch.impress.co.jp》. 2016년 8월 13일에 원본 문서에서 보존된 문서.

- ↑ Beyond 3D의 데이브 바우만(Dave Baumann)을 통한 ATI 엔지니어

- ↑ “2000년부터 2009년까지 자랑스러운 우리의 유산”. 《삼성 반도체》. 삼성. 2019년 6월 25일에 확인함.

- ↑ “삼성 50nm 2GB DDR3 칩은 업계에서 가장 작다”. 《SlashGear》. 2008년 9월 29일. 2019년 6월 25일에 확인함.

- ↑ 가 나 다 “역사: 2010년대”. 《az5miao》. 2022년 4월 4일에 확인함.

- ↑ “2010년부터 현재까지 자랑스러운 우리의 유산”. 《삼성 반도체》. 삼성. 2019년 6월 25일에 확인함.

- ↑ “삼성전자, 5G 및 AI 기반 모바일 애플리케이션용 업계 최초 8Gb LPDDR5 DRAM 발표”. 삼성. 2018년 7월 17일. 2019년 7월 8일에 확인함.

- ↑ “삼성, 넓은 DDR4 256GB RAM 출시”. 《탐스 하드웨어》. 2018년 9월 6일. 2019년 6월 21일에 원본 문서에서 보존된 문서. 2022년 4월 4일에 확인함.

외부 링크

[편집] 위키미디어 공용에 랜덤 액세스 메모리 관련 미디어 자료가 있습니다.

위키미디어 공용에 랜덤 액세스 메모리 관련 미디어 자료가 있습니다.