아날로그-디지털 변환회로

위:연속된 아날로그 신호

아래:이산화된 디지털 신호

아날로그-디지털 변환회로는 A/D 컨버터(Analog-to-digital converter) 또는 간단하게 ADC라 하며, 아날로그 전기 신호를 디지털 전기 신호로 변환하는 전자 회로이다.[1][2] 일렉트로닉스에서 아날로그-디지털 변환회로(ADC, A/D, 또는 A-to-D)는 마이크로폰으로 수집된 소리나 디지털 카메라로 들어오는 빛과 같은 아날로그 신호를 디지털 신호로 변환하는 시스템이다. ADC는 또한 전자 장치가 아날로그 입력 전압 또는 전류를 해당 전압이나 전류의 크기를 나타내는 디지털 숫자로 변환하는 것과 같이 독립적인 측정값을 제공할 수도 있다. 일반적으로 디지털 출력은 입력에 비례하는 2의 보수 이진수이지만, 다른 가능성도 있다.

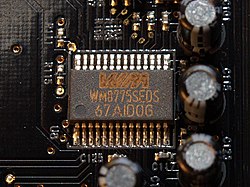

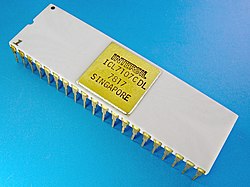

여러 가지 ADC 하드웨어 아키텍처가 있다. 복잡성과 정밀하게 일치해야 하는 전자 부품의 필요성 때문에, 대부분의 특수 ADC를 제외하고는 집적 회로(IC)로 구현된다. 이들은 일반적으로 MOS 혼성 신호 집적 회로 칩 형태로 아날로그 회로와 디지털 회로를 모두 통합한다.

디지털-아날로그 변환회로(DAC)는 역기능을 수행하여 디지털 신호를 아날로그 신호로 변환한다.

아날로그 신호는 저장이나 조작의 편리성이 디지털 신호보다 어렵기 때문에, 초기의 전자공학과 달리 현재는 디지털화를 많이 한다. 신호 전송 시, 일반적으로 아날로그 신호를 디지털 신호로 변환하면 신호의 잡음 등에 유리하다. 다만 변환 시 생기는 왜곡은 감수해야 한다. 따라서 아날로그를 디지털화하여 신호를 조작하고 다시 디지털-아날로그 변환회로(DAC)를 통해 아날로그로 변환한다.

예를 들어 초기의 전화기는 아날로그 방식으로 신호를 전송하였다. 교환망이 진화하면서 음성 신호를 PCM 방식으로 디지털화하고 이것을 전송하며 수신측에서 다시 아날로그로 디코딩한다.

설명

[편집]ADC는 연속 시간 및 연속 진폭의 아날로그 신호를 이산 시간 및 이산 진폭의 디지털 신호로 변환한다. 변환 과정은 입력의 양자화를 포함하므로 필연적으로 소량의 양자화 오차를 발생시킨다. 또한 ADC는 변환을 연속적으로 수행하는 대신 주기적으로 수행하여 입력을 표본화하고 입력 신호의 허용 가능한 대역폭을 제한한다.

ADC의 성능은 주로 대역폭과 신호 대 잡음 및 왜곡비(SNDR)로 특징지어진다. ADC의 대역폭은 주로 샘플링 속도로 특징지어진다. ADC의 SNDR은 해상도, 선형성 및 정확도(양자화 레벨이 실제 아날로그 신호와 얼마나 잘 일치하는지), 에일리어싱 및 지터를 포함한 여러 요인에 의해 영향을 받는다. ADC의 SNDR은 종종 유효 비트 수(ENOB)로 요약되는데, 이는 반환하는 각 측정 비트 중 평균적으로 잡음이 아닌 비트 수를 나타낸다. 이상적인 ADC는 해상도와 동일한 ENOB를 갖는다. ADC는 디지털화할 신호의 대역폭과 요구되는 SNDR에 맞게 선택된다. ADC가 신호 대역폭의 두 배 이상으로 샘플링 속도를 작동하면 나이퀴스트-섀넌 표본화 정리에 따라 거의 완벽한 재구성이 가능하다. 양자화 오차의 존재는 이상적인 ADC조차도 SNDR을 제한한다. 그러나 ADC의 SNDR이 입력 신호의 SNDR을 초과하면 양자화 오차의 영향은 무시될 수 있으며, 결과적으로 대역 제한된 아날로그 입력 신호의 본질적으로 완벽한 디지털 표현이 가능하다.

해상도

[편집]

변환기의 해상도는 허용된 아날로그 입력 값 범위 내에서 생성할 수 있는 서로 다른, 즉 개별 값의 수를 나타낸다. 따라서 특정 해상도는 양자화 오차의 크기를 결정하고, 그 결과 오버샘플링을 사용하지 않는 이상적인 ADC의 최대 가능한 신호 대 잡음비를 결정한다. 입력 샘플은 일반적으로 ADC 내부에 이진 형태로 전자적으로 저장되므로, 해상도는 일반적으로 비트 심도로 표현된다. 결과적으로 사용 가능한 개별 값의 수는 일반적으로 2의 거듭제곱이다. 예를 들어, 8비트 해상도의 ADC는 아날로그 입력을 256가지 다른 레벨 중 하나로 인코딩할 수 있다(28 = 256). 값은 애플리케이션에 따라 0에서 255(즉, 부호 없는 정수) 또는 -128에서 127(즉, 부호 있는 정수)까지의 범위를 나타낼 수 있다.

해상도는 전기적으로도 정의될 수 있으며 볼트로 표현된다. 출력 코드 레벨의 변화를 보장하는 데 필요한 전압 변화를 최하위 비트(LSB) 전압이라고 한다. ADC의 해상도 Q는 LSB 전압과 같다. ADC의 전압 해상도는 전체 전압 측정 범위를 간격 수로 나눈 값과 같다.

여기서 M은 비트 단위의 ADC 해상도이고 EFSR은 전체 범위 전압 범위('스팬'이라고도 함)이다. EFSR은 다음과 같이 주어진다.

여기서 VRefHi 및 VRefLow는 각각 코딩될 수 있는 전압의 상한 및 하한 극값이다.

일반적으로 전압 간격 수는 다음과 같이 주어진다.

여기서 M은 비트 단위의 ADC 해상도이다.[3]

즉, 두 개의 연속적인 코드 레벨 사이에 하나의 전압 간격이 할당된다.

예시:

- 그림 1과 같은 코딩 방식

- 풀 스케일 측정 범위 = 0에서 1볼트

- ADC 해상도 3비트: 23 = 8 양자화 레벨(코드)

- ADC 전압 해상도, Q = 1 V / 8 = 0.125 V.

대부분의 경우 변환기의 유용한 해상도는 신호 대 잡음비(SNR) 및 전체 시스템의 기타 오류(ENOB로 표현됨)에 의해 제한된다.

양자화 오차

[편집]

양자화 오차는 이상적인 ADC에 내재된 양자화에 의해 발생한다. 이는 ADC의 아날로그 입력 전압과 출력 디지털화된 값 사이의 반올림 오차이다. 이 오차는 비선형적이며 신호에 따라 달라진다. 양자화 오차가 -1⁄2 LSB와 +1⁄2 LSB 사이에 균일하게 분포하고, 신호가 모든 양자화 레벨을 포함하는 균일 분포를 가지는 이상적인 ADC에서 신호-양자화 잡음비(SQNR)는 다음과 같이 주어진다.

여기서 은 양자화 비트 수이다. 예를 들어, 16비트 ADC의 경우 양자화 오차는 최대 레벨보다 96.3 dB 낮다.

양자화 오차는 DC에서 나이퀴스트 진동수까지 분포한다. 결과적으로, ADC의 대역폭 중 일부가 사용되지 않는 경우(예: 오버샘플링의 경우), 양자화 오차의 일부는 대역외에서 발생하여 사용 중인 대역폭의 SQNR을 효과적으로 향상시킨다. 오버샘플링 시스템에서는 노이즈 셰이핑을 사용하여 더 많은 양자화 오차를 대역 밖으로 밀어내어 SQNR을 더욱 증가시킬 수 있다.

디더링

[편집]ADC에서는 일반적으로 디더링을 사용하여 성능을 향상시킬 수 있다. 이것은 변환 전에 입력에 추가되는 아주 작은 양의 무작위 잡음(예: 백색 잡음)이다. 그 효과는 신호에 따라 LSB의 상태를 무작위화하는 것이다. 신호가 낮은 레벨에서 완전히 잘리는 대신, 약간의 잡음 증가를 대가로 ADC가 변환할 수 있는 신호의 유효 범위를 확장한다. 디더링은 샘플러의 해상도를 높일 수만 있다. 선형성을 향상시킬 수는 없으므로 정확도가 반드시 향상되는 것은 아니다.

ADC의 비트 심도에 비해 매우 낮은 레벨의 음성 신호에서 발생하는 양자화 왜곡은 신호와 상관 관계가 있으며 왜곡되고 불쾌하게 들린다. 디더링을 사용하면 왜곡이 잡음으로 변환된다. 왜곡되지 않은 신호는 시간 경과에 따른 평균화를 통해 정확하게 복구될 수 있다. 디더링은 전력량계와 같은 통합 시스템에서도 사용된다. 값들이 함께 추가되므로 디더링은 아날로그-디지털 변환기의 LSB보다 더 정확한 결과를 생성한다.

사진 이미지의 픽셀당 비트 수를 줄여 양자화할 때 디더링이 자주 적용된다. 이미지는 더 시끄러워지지만, 눈에는 양자화된 이미지보다 훨씬 더 사실적으로 보인다. 양자화된 이미지는 그렇지 않으면 밴딩 현상이 나타난다. 이 유사한 프로세스는 디지털로 변환되는 아날로그 음성 신호에 대한 디더링의 효과를 시각화하는 데 도움이 될 수 있다.

정확도

[편집]ADC에는 여러 가지 오차 원인이 있다. 양자화 오차와 (ADC가 선형이라고 가정할 경우) 비선형성은 모든 아날로그-디지털 변환에 본질적이다. 이러한 오차는 최하위 비트(LSB)라는 단위로 측정된다. 위 8비트 ADC의 예에서, 1 LSB의 오차는 전체 신호 범위의 1⁄256 또는 약 0.4%이다.

비선형성

[편집]모든 ADC는 물리적 불완전성으로 인한 비선형성 오차를 겪는다. 이는 출력이 입력의 선형 함수(또는 의도적으로 비선형적인 ADC의 경우 다른 함수)에서 벗어나게 한다. 이러한 오차는 때때로 교정으로 완화되거나 테스트로 방지할 수 있다. 선형성에 대한 중요한 매개변수는 적분 비선형성과 미분 비선형성이다. 이러한 비선형성은 ADC의 신호 대 잡음비 성능을 저하시키고 결과적으로 유효 해상도를 감소시킬 수 있는 왜곡을 유발한다.

지터

[편집]사인파 를 디지털화할 때, 비이상적인 샘플링 클럭을 사용하면 샘플이 기록되는 시점에 불확실성이 발생한다. 클럭 지터로 인한 실제 샘플링 시간 불확실성이 일 때, 이 현상으로 인한 오차는 로 추정할 수 있다. 이는 추가적인 기록된 잡음을 유발하여 양자화 오차만으로 예측되는 유효 비트 수(ENOB)를 감소시킨다. 이 오차는 DC에서는 0이고 낮은 주파수에서는 작지만, 높은 진폭과 높은 주파수 신호에서는 상당하다. 지터가 성능에 미치는 영향은 양자화 오차와 비교할 수 있다. 여기서 q는 ADC 비트 수이다.

| 출력 크기 (비트) |

신호 주파수 | ||||||

|---|---|---|---|---|---|---|---|

| 1 Hz | 1 kHz | 10 kHz | 1 MHz | 10 MHz | 100 MHz | 1 GHz | |

| 8 | 1,243 μs | 1.24 μs | 124 ns | 1.24 ns | 124 ps | 12.4 ps | 1.24 ps |

| 10 | 311 μs | 311 ns | 31.1 ns | 311 ps | 31.1 ps | 3.11 ps | 0.31 ps |

| 12 | 77.7 μs | 77.7 ns | 7.77 ns | 77.7 ps | 7.77 ps | 0.78 ps | 0.08 ps (77.7 fs) |

| 14 | 19.4 μs | 19.4 ns | 1.94 ns | 19.4 ps | 1.94 ps | 0.19 ps | 0.02 ps (19.4 fs) |

| 16 | 4.86 μs | 4.86 ns | 486 ps | 4.86 ps | 0.49 ps | 0.05 ps (48.5 fs) | – |

| 18 | 1.21 μs | 1.21 ns | 121 ps | 1.21 ps | 0.12 ps | – | – |

| 20 | 304 ns | 304 ps | 30.4 ps | 0.30 ps (303.56 fs) | 0.03 ps (30.3 fs) | – | – |

| 24 | 18.9 ns | 18.9 ps | 1.89 ps | 0.019 ps (18.9 fs) | - | – | – |

클럭 지터는 위상 잡음에 의해 발생한다.[5][6] 1 MHz에서 1 GHz 사이의 디지털화 대역폭을 가진 ADC의 해상도는 지터에 의해 제한된다.[7] 44.1 kHz와 같은 음성 신호를 샘플링하는 것과 같이 낮은 대역폭 변환의 경우, 클럭 지터가 성능에 미치는 영향은 덜 중요하다.[8]

샘플링 속도

[편집]아날로그 신호는 시간에 따라 연속적이며, 이를 디지털 값의 흐름으로 변환해야 한다. 따라서 아날로그 신호에서 새로운 디지털 값이 샘플링되는 속도를 정의해야 한다. 새로운 값의 속도를 변환기의 샘플링 속도 또는 샘플링 주파수라고 한다. 연속적으로 변화하는 대역 제한 신호는 표본화될 수 있으며, 그 다음 재구성 필터를 통해 이산 시간 값으로부터 원본 신호를 재현할 수 있다. 나이퀴스트-섀넌 표본화 정리는 원본 신호의 충실한 재현은 샘플링 속도가 신호의 최고 주파수의 두 배보다 높을 때만 가능하다는 것을 의미한다.

실제 ADC는 즉각적인 변환을 할 수 없으므로, 변환기가 변환을 수행하는 동안 (변환 시간이라고 함) 입력 값은 반드시 일정하게 유지되어야 한다. 샘플 앤 홀드라고 불리는 입력 회로는 이 작업을 수행하는데, 대부분의 경우 축전기를 사용하여 입력의 아날로그 전압을 저장하고, 전자 스위치 또는 게이트를 사용하여 축전기를 입력에서 분리한다. 많은 ADC 집적 회로는 샘플 앤 홀드 서브시스템을 내부에 포함한다.

에일리어싱

[편집]ADC는 특정 시간 간격으로 입력 값을 표본화하여 작동한다. 관심 있는 최고 주파수의 두 배로 정의되는 나이퀴스트율보다 높은 속도로 입력이 샘플링되면, 신호 내의 모든 주파수가 재구성될 수 있다. 나이퀴스트율의 절반을 초과하는 주파수가 샘플링되면, 이는 더 낮은 주파수로 잘못 감지되는데, 이 과정을 에일리어싱이라고 한다. 에일리어싱은 주기당 두 번 이하로 함수를 즉각적으로 샘플링하면 주기를 놓치게 되어 잘못된 낮은 주파수가 나타나기 때문에 발생한다. 예를 들어, 1.5 kHz로 샘플링되는 2 kHz 사인파는 500 Hz 사인파로 재구성된다.

에일리어싱을 방지하려면 ADC의 입력은 샘플링 속도의 절반을 초과하는 주파수를 제거하기 위해 로우패스 필터를 통과해야 한다. 이 필터를 위신호 제거라고 하며, 더 높은 주파수 내용을 가진 아날로그 신호에 적용되는 실제 ADC 시스템에 필수적이다. 에일리어싱 방지가 필수적인 응용 분야에서는 오버샘플링을 사용하여 이를 크게 줄이거나 심지어 제거할 수도 있다.

대부분의 시스템에서 에일리어싱은 원치 않지만, 대역 제한된 고주파 신호의 동시 다운믹싱을 제공하는 데 활용될 수 있다(언더샘플링 및 주파수 믹서 참조). 에일리어스는 사실상 신호 주파수와 샘플링 주파수의 낮은 헤테로다인이다.[9]

오버샘플링

[편집]경제성을 위해 신호는 종종 필요한 최소 속도로 샘플링되며, 그 결과 도입되는 양자화 오차는 변환기의 전체 통과대역에 걸쳐 퍼져 있는 백색 잡음이다. 신호가 나이퀴스트율보다 훨씬 높은 속도로 샘플링된 다음 디지털 필터를 사용하여 신호 대역폭으로 제한되면 다음과 같은 이점이 발생한다.

오버샘플링은 일반적으로 오디오 주파수 ADC에서 사용되는데, 필요한 샘플링 속도(일반적으로 44.1 또는 48kHz)가 일반적인 트랜지스터 회로의 클럭 속도(>1MHz)에 비해 매우 낮기 때문이다. 이 경우 ADC의 성능은 비용을 거의 들이지 않고도 크게 향상될 수 있다. 또한, 모든 에일리어스 신호도 일반적으로 대역외에 있으므로, 매우 저렴한 필터를 사용하여 에일리어싱을 종종 제거할 수 있다.

상대적인 속도와 정밀도

[편집]ADC의 속도는 유형에 따라 다르다. 윌킨슨 ADC는 현재 디지털 회로로 처리할 수 있는 클럭 속도에 의해 제한된다. 축차 비교형 ADC의 경우, 변환 시간은 해상도의 로그(즉, 비트 수)에 비례한다. 플래시 ADC는 세 가지 유형 중 확실히 가장 빠르다. 변환은 기본적으로 단일 병렬 단계로 수행된다.

속도와 정밀도 사이에는 잠재적인 균형이 있다. 플래시 ADC는 비교기 레벨과 관련된 표류 및 불확실성으로 인해 선형성이 좋지 않다. 정도는 덜하지만, 축차 비교형 아날로그-디지털 변환회로에서도 선형성 문제가 발생할 수 있다. 여기서 비선형성은 감산 과정에서 발생하는 누적 오차로 인해 발생한다. 윌킨슨 ADC는 세 가지 유형 중 가장 우수한 선형성을 가지고 있다.[10][11]

슬라이딩 스케일 원리

[편집]슬라이딩 스케일 또는 무작위화 방법은 모든 유형의 ADC, 특히 플래시 및 축차 근사 유형의 선형성을 크게 향상시키는 데 사용될 수 있다. 어떤 ADC에서든 입력 전압에서 디지털 출력 값으로의 매핑은 정확히 바닥 함수 또는 천장 함수가 아니다. 정상적인 조건에서는 특정 진폭의 펄스가 항상 동일한 디지털 값으로 변환된다. 문제는 디지털화된 값의 아날로그 값 범위가 모두 동일한 너비를 가지지 않으며, 미분 선형성은 평균 너비에서 벗어나는 정도에 비례하여 감소한다는 것이다. 슬라이딩 스케일 원리는 이러한 현상을 극복하기 위해 평균화 효과를 사용한다. 무작위적이지만 알려진 아날로그 전압이 샘플링된 입력 전압에 추가된다. 그런 다음 디지털 형식으로 변환되고, 해당 디지털 양이 빼져 원래 값으로 복원된다. 장점은 변환이 임의의 지점에서 일어난다는 것이다. 최종 레벨의 통계적 분포는 ADC 범위의 한 영역에 걸쳐 가중 평균에 의해 결정된다. 이는 결국 특정 레벨의 너비에 대한 민감도를 감소시킨다.[12][13]

변환 방식

[편집]| 이름 | 속도 | 해상도 | 특징 | 용도 |

|---|---|---|---|---|

| 플래시형 (병렬 비교형) |

10G~10M | 12~6 | 고속, 대규모 | 고속 측정기 |

| 파이프라인형 | 150M~10M | 14~8 | 영상 신호처리 | |

| 축차 비교형 | 1M~10k | 16~8 | 낮은 소비전력 | 마이크로컨트롤러 |

| 델타시그마형 | 100k~100M | 24~18 | 높은 분해력 | 음성 처리 |

| 이중 적분형 | 1k~10 | 22~12 | 고정밀 | 측정기 |

RC 충전 시간

[편집]RC 회로는 알려진 전압 충전 및 방전 곡선을 가지며, 이를 사용하여 미지의 아날로그 값을 해결할 수 있다.

윌킨슨 방식

[편집]윌킨슨 ADC는 1950년 데니스 윌킨슨이 설계했다. 윌킨슨 ADC는 입력 전압과 충전 중인 축전기에서 생성되는 전압을 비교하는 방식이다. 축전기는 비교기가 입력 전압과 일치한다고 판단할 때까지 충전된다. 그런 다음, 정전류원을 사용하여 축전기가 선형적으로 방전된다. 축전기를 방전하는 데 걸리는 시간은 입력 전압의 진폭에 비례한다. 축전기가 방전되는 동안, 고주파 발진기 클럭에서 나오는 펄스는 레지스터에 의해 계수된다. 레지스터에 기록된 클럭 펄스 수는 입력 전압에 비례한다.[14][15]

아날로그 저항 또는 커패시턴스 측정

[편집]측정할 아날로그 값이 저항 또는 커패시턴스로 표현되는 경우, 해당 요소를 RC 회로에 포함시키고(다른 저항 또는 커패시턴스는 고정된 상태로) 알려진 전압 공급 장치에서 저항을 통해 알려진 시작 전압에서 다른 알려진 종료 전압까지 커패시턴스를 충전하는 데 걸리는 시간을 측정함으로써, 축전기 충전 방정식을 사용하여 미지의 저항 또는 커패시턴스 값을 결정할 수 있다.

그리고 이 시작 및 종료 데이터 포인트를 사용하여 미지의 저항 또는 커패시턴스를 구한다. 이는 알려진 저항과 커패시턴스로 미지의 전압을 측정하는 윌킨슨 ADC와 유사하지만 대조적으로, 대신 알려진 전압으로 미지의 저항 또는 커패시턴스를 측정한다.

예를 들어, 단일 안정 또는 비안정 모드의 555 타이머 IC의 양수(및 음수) 펄스 폭은 커패시터가 Vsupply의 1⁄3에서 Vsupply의 2⁄3까지 충전(및 방전)하는 데 걸리는 시간을 나타낸다. 이 펄스를 정확한 클럭이 있는 마이크로컨트롤러로 전송함으로써, 펄스의 지속 시간을 측정하고 축전기 충전 방정식을 사용하여 미지의 저항 또는 커패시턴스 값을 생성할 수 있다.

더 큰 저항과 커패시턴스는 더 작은 것보다 측정 시간이 더 오래 걸린다. 그리고 정확도는 마이크로컨트롤러 클럭의 정확도와 값을 측정하는 데 사용 가능한 시간의 양에 의해 제한되며, 이는 측정 중에도 변경되거나 외부 기생 요소의 영향을 받을 수 있다.

플래시 ADC

[편집]병렬 탐색 ADC라고도 하는 플래시 ADC는[16] 각각 다른 전압 임계값을 가진 전압 비교기 뱅크를 사용하여 입력 신호를 병렬로 샘플링한다. 회로는 저항 분배기 네트워크, 전압 비교기 세트, 그리고 우선 순위 인코더로 구성된다. 저항 분배기의 각 노드는 하나의 비교기에 대한 전압 임계값을 제공한다. 비교기 출력은 우선 순위 인코더에 적용되어 입력 전압에 비례하는 이진수를 생성한다.

플래시 ADC는 다이 크기가 크고 전력 소모가 많다. 이들은 비디오, 광대역 통신, 그리고 다른 빠른 신호를 디지털화하는 것을 포함한 다양한 응용 분야에서 사용된다.

이 회로는 변환이 순차적으로가 아니라 동시에 이루어지므로 고속이라는 장점이 있다. 일반적인 변환 시간은 100 ns 이내이다. 변환 시간은 비교기와 우선 순위 인코더의 속도에 의해서만 제한된다. 이 유형의 ADC는 출력 비트가 하나씩 추가될 때마다 필요한 비교기의 수가 거의 두 배가 되고 우선 순위 인코더가 더 복잡해진다는 단점이 있다.

축차 비교형

[편집]축차 비교형 아날로그-디지털 변환회로는 비교기와 이진 검색을 사용하여 입력 전압을 포함하는 범위를 연속적으로 좁힌다. 각 연속 단계에서 변환기는 입력 전압을 내부 DAC의 출력과 비교하는데, 이 DAC는 처음에 허용된 입력 전압 범위의 중간 지점을 나타낸다. 이 과정의 각 단계에서 근사치는 축차 근사 레지스터(SAR)에 저장되고, 디지털-아날로그 변환기의 출력은 더 좁은 범위에서 비교를 위해 업데이트된다.

램프-비교형

[편집]램프-비교형 ADC는 톱니형 신호를 생성하여 위아래로 램프를 올리거나 내린 다음 빠르게 0으로 돌아간다.[17] 램프가 시작되면 타이머가 카운트를 시작한다. 램프 전압이 입력과 일치하면 비교기가 작동하고 타이머 값이 기록된다. 시간 제한 램프 변환기는 경제적으로 구현될 수 있지만,[a] 램프를 생성하는 회로가 종종 단순한 아날로그 적분기이기 때문에 램프 시간은 온도에 민감할 수 있다. 더 정확한 변환기는 DAC를 구동하는 클럭 카운터를 사용한다. 램프-비교 시스템의 특별한 장점은 두 번째 신호를 변환하는 데 또 다른 비교기와 타이머 값을 저장할 다른 레지스터만 있으면 된다는 것이다. 변환 중 입력 변화에 대한 민감도를 줄이기 위해 샘플 앤 홀드는 순간 입력 전압으로 축전기를 충전할 수 있으며, 변환기는 정전류원으로 방전하는 데 필요한 시간을 측정할 수 있다.

적분형

[편집]적분형 ADC(또한 이중 경사 또는 다중 경사 ADC)는 미지의 입력 전압을 적분기의 입력에 인가하고 전압이 고정된 시간 동안(상승 기간) 램프를 그리도록 허용한다. 그런 다음 반대 극성의 알려진 기준 전압이 적분기에 인가되고 적분기 출력이 0으로 돌아올 때까지(하강 기간) 램프를 그리도록 허용된다. 입력 전압은 기준 전압, 고정된 상승 시간 기간, 그리고 측정된 하강 시간 기간의 함수로 계산된다. 하강 시간 측정은 일반적으로 변환기 클럭 단위로 이루어지므로, 더 긴 적분 시간은 더 높은 해상도를 허용한다. 마찬가지로, 해상도를 희생하여 변환기의 속도를 향상시킬 수 있다. 이 유형의 변환기(또는 개념의 변형)는 대부분의 디지털 전압계에서 선형성과 유연성 때문에 사용된다.

- 전하 균형 ADC

- 전하 균형 ADC의 원리는 먼저 입력 신호를 전압-주파수 변환기를 사용하여 주파수로 변환하는 것이다. 이 주파수는 주파수 계수기로 측정되어 아날로그 입력에 비례하는 출력 코드로 변환된다. 이 변환기의 주요 장점은 잡음이 많은 환경이나 절연된 형태로도 주파수를 전송할 수 있다는 것이다. 그러나 이 회로의 한계는 전압-주파수 변환기의 출력이 RC 제품에 의존하는데, 이 값은 온도 및 시간에 따라 정확하게 유지될 수 없다는 점이다.

- 이중 경사 ADC

- 회로의 아날로그 부분은 높은 입력 임피던스 버퍼, 정밀 적분기 및 전압 비교기로 구성된다. 변환기는 먼저 고정된 시간 동안 아날로그 입력 신호를 적분한 다음, 적분기 출력이 0이 될 때까지 반대 극성의 내부 기준 전압을 적분한다. 이 회로의 주요 단점은 긴 지속 시간이다. 이들은 열전대 및 저울과 같이 느리게 변하는 신호의 정확한 측정에 특히 적합하다.

델타 인코딩

[편집]델타 인코딩 또는 카운터 램프 ADC는 DAC에 공급되는 상하 카운터를 가지고 있다. 입력 신호와 DAC는 모두 비교기로 들어간다. 비교기는 카운터를 제어한다. 이 회로는 비교기로부터의 음성 되먹임을 사용하여 DAC의 출력이 입력 신호와 일치할 때까지 카운터를 조정하고, 그 숫자는 카운터에서 읽힌다. 델타 변환기는 매우 넓은 범위와 높은 해상도를 가지지만, 변환 시간은 입력 신호 동작에 따라 달라지며, 최악의 경우에도 항상 보장된 값을 가진다. 델타 변환기는 물리적 시스템의 대부분의 신호가 갑자기 변하지 않으므로 실제 신호를 읽는 데 매우 좋은 선택이다. 일부 변환기는 델타와 축차 근사 방법을 결합한다. 이는 입력 신호의 고주파 성분이 크기가 작은 것으로 알려져 있을 때 특히 효과적이다.

파이프라인형

[편집]파이프라인형 ADC(서브레인징 양자화기라고도 함)는 두 개 이상의 변환 단계를 사용한다. 먼저, 대략적인 변환이 수행된다. 두 번째 단계에서는 DAC를 사용하여 입력 신호와의 차이가 결정된다. 이 차이는 더 정밀하게 변환되고, 결과는 마지막 단계에서 결합된다. 이는 축차 비교형 아날로그-디지털 변환회로의 정교화로 볼 수 있는데, 여기서 피드백 기준 신호는 다음으로 가장 중요한 비트가 아니라 전체 비트 범위(예: 4비트)의 중간 변환으로 구성된다. 축차 근사 및 플래시 ADC의 장점을 결합함으로써 이 유형은 빠르고, 높은 해상도를 가지며, 효율적으로 구현될 수 있다.

델타-시그마

[편집]델타-시그마 ADC(또는 시그마-델타 ADC)는 아날로그 필터와 저해상도(종종 1비트)이지만 높은 샘플링 속도 ADC 및 DAC를 가진 음성 되먹임 루프를 기반으로 한다. 피드백 루프는 누적된 양자화 오류를 지속적으로 수정하고 노이즈 셰이핑을 수행한다. 즉, 관심 있는 낮은 주파수에서는 양자화 잡음이 감소하지만, 높은 주파수에서는 증가한다. 그런 다음 이러한 높은 주파수는 다운샘플링 디지털 필터에 의해 제거될 수 있으며, 이 필터는 또한 데이터 스트림을 높은 샘플링 속도와 낮은 비트 심도에서 더 높은 비트 심도의 낮은 속도로 변환한다.

시분할 다중화

[편집]시분할 다중화 ADC는 M개의 병렬 ADC를 사용하는데, 각 ADC는 유효 샘플 클럭의 M번째 주기마다 데이터를 샘플링한다. 그 결과 각 개별 ADC가 처리할 수 있는 샘플링 속도보다 M배 증가한다. 실제로는 M개의 ADC 간의 개별 차이로 인해 전체 성능이 저하되어 SFDR(스퓨리어스 프리 다이내믹 레인지)이 감소한다.[19] 그러나 이러한 시분할 다중화 불일치 오류를 수정하는 기술이 존재한다.[20]

중간 FM 단계

[편집]중간 FM 단계를 갖춘 ADC는 먼저 전압-주파수 변환기를 사용하여 입력 신호의 전압에 비례하는 주파수를 가진 발진 신호를 생성하고, 그런 다음 주파수 계수기를 사용하여 그 주파수를 원하는 신호 전압에 비례하는 디지털 카운트로 변환한다. 통합 시간이 길수록 해상도가 높아진다. 마찬가지로 해상도를 희생하여 변환기의 속도를 향상시킬 수 있다. ADC의 두 부분은 넓게 분리되어 포토 커플러를 통해 주파수 신호가 전달되거나 무선으로 전송될 수 있다. 일부 ADC는 사인파 또는 구형파 주파수 변조를 사용하고, 다른 ADC는 펄스-주파수 변조를 사용한다. 이러한 ADC는 한때 원격 아날로그 센서의 상태를 디지털 디스플레이로 보여주는 가장 인기 있는 방법이었다.[21][22][23][24][25]

시간 지연

[편집]시간 지연 아날로그-디지털 변환회로(TS-ADC)는 기존 전자 ADC로는 디지털화할 수 없는 매우 넓은 대역폭의 아날로그 신호를 디지털화하기 위해 디지털화 전에 신호를 시간 지연시킨다. 일반적으로 광자 전처리기를 사용하여 신호를 시간 지연시키는데, 이는 신호를 시간적으로 늦추고 대역폭을 압축하는 효과를 가진다. 그 결과, 원래 신호를 포착하기에는 너무 느렸을 전자 ADC가 이제 이 느려진 신호를 포착할 수 있다. 신호의 연속적인 포착을 위해 전단부는 시간 지연 외에도 신호를 여러 세그먼트로 나눈다. 각 세그먼트는 별도의 전자 ADC에 의해 개별적으로 디지털화된다. 마지막으로, 디지털 신호 처리 장치는 샘플을 재정렬하고 전처리기에서 추가된 모든 왜곡을 제거하여 원본 아날로그 신호의 디지털 표현인 이진 데이터를 생성한다.

전압 이외의 물리적 값 측정

[편집]ADC라는 용어는 일반적으로 아날로그 전압 측정과 관련되지만, 측정 가능한 물리적 아날로그 양을 디지털 숫자로 변환하는 일부 부분 전자 장치도 ADC로 간주될 수 있다. 예를 들면 다음과 같다.

- 로터리 인코더는 기계적으로 회전량을 생성하는 아날로그 물리량을 그레이 부호의 디지털 스트림으로 변환하며, 마이크로컨트롤러는 이를 디지털 방식으로 해석하여 회전 방향, 각 위치, 회전 속도를 도출할 수 있다.[26]

- 정전식 감응은 커패시턴스라는 아날로그 물리량을 변환한다. 이 커패시턴스는 금속 물체가 금속 감지 플레이트에서 떨어진 거리, 탱크 안의 물의 양, 유전체 물질의 유전율과 같은 다른 물리량의 대리 변수가 될 수 있다.

- 디지털 캘리퍼스는 두 개의 슬라이딩 자 사이에 변위량이라는 아날로그 물리량을 변환한다.

- 유도-디지털 변환기는 교류 자기장 내에서 움직이는 전도성 목표물에 의해 발생하는 유도계수의 변화를 측정한다.[28]

- 시간-디지털 변환기는 이벤트를 인식하고 그 이벤트가 발생한 시간의 디지털 표현을 제공한다.

- 일반적으로 전압을 직접 생성하지 않는 센서는 간접적으로 전압을 생성하거나 다른 방법으로 디지털 값으로 변환될 수 있다.

상업용

[편집]많은 경우, 집적 회로에서 가장 비싼 부분은 핀이다. 핀은 패키지를 더 크게 만들고, 각 핀은 집적 회로의 실리콘에 연결되어야 하기 때문이다. 핀을 절약하기 위해 ADC는 일반적으로 클럭 신호가 상태를 변경할 때마다 비트 단위로 데이터를 직렬 인터페이스를 통해 컴퓨터로 전송한다. 이는 ADC 패키지에서 상당한 수의 핀을 절약하며, 많은 경우 전체 설계를 더 복잡하게 만들지 않는다.

상업용 ADC는 종종 동일한 변환기에 여러 입력이 연결되어 있으며, 일반적으로 아날로그 멀티플렉서를 통해 연결된다. ADC의 다양한 모델에는 샘플 앤 홀드 회로, 계측 앰프 또는 차동 입력이 포함될 수 있으며, 여기서 측정되는 양은 두 입력 간의 차이이다.

응용 분야

[편집]음악 녹음

[편집]아날로그-디지털 변환기는 현대 음악 재생 기술과 디지털 오디오 워크스테이션 기반 녹음에 필수적이다. 음악은 아날로그 녹음을 사용하여 컴퓨터에서 제작될 수 있으므로 콤팩트 디스크와 디지털 음악 파일에 들어가는 펄스 부호 변조(PCM) 데이터 스트림을 생성하려면 아날로그-디지털 변환기가 필요하다. 현재 음악에 사용되는 아날로그-디지털 변환기는 최대 192 킬로헤르츠의 속도로 샘플링할 수 있다. 많은 녹음 스튜디오는 24비트 96 kHz 펄스 부호 변조(PCM) 형식으로 녹음한 다음 다운샘플링하고 신호를 콤팩트 디스크 디지털 오디오 제작(44.1 kHz) 또는 라디오 및 텔레비전 방송 응용 분야(48 kHz)를 위해 디더링한다.

디지털 신호 처리

[편집]ADC는 사실상 모든 아날로그 신호를 디지털 형태로 처리, 저장 또는 전송하는 디지털 신호 처리 시스템에 필수적이다. 예를 들어, TV 수신 카드는 고속 비디오 아날로그-디지털 변환기를 사용한다. 온칩의 느린 8비트, 10비트, 12비트 또는 16비트 아날로그-디지털 변환기는 마이크로컨트롤러에서 흔히 볼 수 있다. 디지털 오실로스코프는 매우 빠른 아날로그-디지털 변환기가 필요하며, 소프트웨어 정의 라디오와 그 새로운 응용 분야에도 중요하다.

과학 기기

[편집]디지털 이미징 시스템은 일반적으로 화소를 디지털화하기 위해 아날로그-디지털 변환기를 사용한다. 일부 레이더 시스템은 신호 강도를 디지털 값으로 변환하여 후속 신호 처리를 위해 아날로그-디지털 변환기를 사용한다. 많은 다른 현장 및 원격탐사 시스템도 유사한 기술을 흔히 사용한다.

과학 기기의 많은 센서는 아날로그 신호를 생성한다. 온도, 압력, pH, 빛의 강도 등. 이러한 모든 신호는 증폭되어 ADC에 공급되어 디지털 표현을 생성할 수 있다.

디스플레이

[편집]평판 디스플레이는 본질적으로 디지털이며 컴포지트 비디오 또는 VGA와 같은 아날로그 신호를 처리하기 위해 ADC가 필요하다.

전기 기호

[편집]시험

[편집]아날로그-디지털 변환기를 테스트하려면 아날로그 입력 소스와 제어 신호를 보내고 디지털 데이터 출력을 캡처하는 컴퓨터 하드웨어가 필요하다. 일부 ADC는 또한 정확한 기준 신호 소스를 요구한다.

ADC를 테스트하는 주요 매개변수는 다음과 같다.

같이 보기

[편집]내용주

[편집]각주

[편집]- ↑ 《Data Conversion Handbook》 (PDF). 2022년 9월 27일에 원본 문서 (PDF)에서 보존된 문서. 2018년 4월 28일에 확인함.

- ↑ 《Principles of Data Acquisition and Conversion》 (PDF). Texas Instruments. April 2015. 2016년 10월 18일에 확인함.

- ↑ “Principles of Data Acquisition and Conversion” (PDF). Texas Instruments. April 2015. 2022년 10월 9일에 원본 문서 (PDF)에서 보존된 문서. 2016년 10월 18일에 확인함.

- ↑ Lathi, B.P. (1998). 《Modern Digital and Analog Communication Systems》 3판. Oxford University Press.

- ↑ “Maxim App 800: Design a Low-Jitter Clock for High-Speed Data Converters”, 《maxim-ic.com》, 2002년 7월 17일

- ↑ “Jitter effects on Analog to Digital and Digital to Analog Converters” (PDF). 2012년 8월 19일에 확인함.

- ↑ Löhning, Michael; Fettweis, Gerhard (2007). 《The effects of aperture jitter and clock jitter in wideband ADCs》. 《Computer Standards & Interfaces Archive》 29. 11–18쪽. CiteSeerX 10.1.1.3.9217. doi:10.1016/j.csi.2005.12.005.

- ↑ Redmayne, Derek; Steer, Alison (2008년 12월 8일), “Understanding the effect of clock jitter on high-speed ADCs”, 《eetimes.com》

- ↑ “RF-Sampling and GSPS ADCs – Breakthrough ADCs Revolutionize Radio Architectures” (PDF). Texas Instruments. 2022년 10월 9일에 원본 문서 (PDF)에서 보존된 문서. 2013년 11월 4일에 확인함.

- ↑ Knoll (1989, 664–665쪽)

- ↑ Nicholson (1974, 313–315쪽)

- ↑ Knoll (1989, 665–666쪽)

- ↑ Nicholson (1974, 315–316쪽)

- ↑ Knoll (1989, 663–664쪽)

- ↑ Nicholson (1974, 309–310쪽)

- ↑ Pelgrom, Marcel J.M. (2022). 〈13.1 Classification of Analog-to-Digital Converters〉 4판. 《Analog-to-Digital Conversion》. Springer International Publishing. 643–645쪽. doi:10.1007/978-3-030-90808-9. ISBN 9783030908089.

- ↑ Couch - 2001 - Digital and analog communication systems - Prentice Hall - New Jersey, USA

- ↑ “Atmel Application Note AVR400: Low Cost A/D Converter” (PDF). 《atmel.com》. 2022년 10월 9일에 원본 문서 (PDF)에서 보존된 문서.

- ↑ Vogel, Christian (2005). 《The Impact of Combined Channel Mismatch Effects in Time-interleaved ADCs》. 《IEEE Transactions on Instrumentation and Measurement》 55. 415–427쪽. Bibcode:2005ITIM...54..415V. CiteSeerX 10.1.1.212.7539. doi:10.1109/TIM.2004.834046. S2CID 15038020.

- ↑ 가브리엘레 망가나로; 데이비드 H. 로버트슨 (July 2015), 《Interleaving ADCs: Unraveling the Mysteries》, 아날로그 디바이스, 2021년 10월 7일에 확인함

- ↑ Analog Devices MT-028 Tutorial: "Voltage-to-Frequency Converters" by Walt Kester and James Bryant 2009, apparently adapted from Kester, Walter Allan (2005) Data conversion handbook, Newnes, p. 274, ISBN 0750678410.

- ↑ Microchip AN795 "Voltage to Frequency / Frequency to Voltage Converter" p. 4: "13-bit A/D converter"

- ↑ Carr, Joseph J. (1996) Elements of electronic instrumentation and measurement, Prentice Hall, p. 402, ISBN 0133416860.

- ↑ "Voltage-to-Frequency Analog-to-Digital Converters". globalspec.com

- ↑ Pease, Robert A. (1991) Troubleshooting Analog Circuits, Newnes, p. 130, ISBN 0750694998.

- ↑ “How to Use Rotary Encoders to Quickly Convert Mechanical Rotation into Digital Signals”. 《Techbriefs》. 2019년 10월 1일. 2023년 10월 9일에 확인함.

- ↑ Jia, Ning (2012년 5월 1일). “ADI Capacitance-to-Digital Converter Technology in Healthcare Applications”. 《아날로그 대화》. 2023년 7월 7일에 원본 문서에서 보존된 문서. 2023년 10월 9일에 확인함.

- ↑ Kasemsadeh, Ben (2015년 7월 31일). “How To Sense Lateral Movement Using An Inductance-to-Digital Converter”. 《Fierce Electronics》. 2023년 10월 9일에 원본 문서에서 보존된 문서. 2023년 10월 9일에 확인함.

- Knoll, Glenn F. (1989). 《Radiation Detection and Measurement》 2판. New York: John Wiley & Sons. ISBN 978-0471815044.

- Nicholson, P. W. (1974). 《Nuclear Electronics》. New York: John Wiley & Sons. 315–316쪽. ISBN 978-0471636977.

더 읽어보기

[편집]- Allen, Phillip E.; Holberg, Douglas R. (2002). 《CMOS Analog Circuit Design》. ISBN 978-0-19-511644-1.

- Fraden, Jacob (2010). 《Handbook of Modern Sensors: Physics, Designs, and Applications》. Springer. ISBN 978-1441964656.

- Kester, Walt 편집 (2005). 《The Data Conversion Handbook》. Elsevier: Newnes. ISBN 978-0-7506-7841-4.

- Johns, David; Martin, Ken (1997). 《Analog Integrated Circuit Design》. Wiley. ISBN 978-0-471-14448-9.

- Liu, Mingliang (2006). 《Demystifying Switched-Capacitor Circuits》. Newnes. ISBN 978-0-7506-7907-7.

- Norsworthy, Steven R.; Schreier, Richard; Temes, Gabor C. (1997). 《Delta-Sigma Data Converters》. IEEE Press. ISBN 978-0-7803-1045-2.

- Razavi, Behzad (1995). 《Principles of Data Conversion System Design》. New York, NY: IEEE Press. ISBN 978-0-7803-1093-3.

- Ndjountche, Tertulien (2011년 5월 24일). 《CMOS Analog Integrated Circuits: High-Speed and Power-Efficient Design》. Boca Raton, FL: CRC Press. ISBN 978-1-4398-5491-4.

- Staller, Len (2005년 2월 24일). 《Understanding analog to digital converter specifications》. 《Embedded Systems Design》.

- Walden, R. H. (1999). 《Analog-to-digital converter survey and analysis》. 《IEEE Journal on Selected Areas in Communications》 17. 539–550쪽. CiteSeerX 10.1.1.352.1881. doi:10.1109/49.761034.

외부 링크

[편집]- 델타 시그마 변환기 소개 델타-시그마 변환기 이론에 대한 매우 좋은 개요이다.

- FFT/DFT 분석 기반 평가 소프트웨어를 통한 A/D 변환 시스템의 디지털 동적 분석 RF 엑스포 이스트, 1987년

- 어떤 ADC 아키텍처가 귀하의 애플리케이션에 적합한가? 월트 케스터의 기사

- ADC 및 DAC 용어집 - 웨이백 머신 (보관됨 2009-11-24) 일반적으로 사용되는 기술 용어를 정의한다.

- AVR의 ADC 소개 – Atmel 마이크로컨트롤러를 사용한 아날로그-디지털 변환

- 시분할 다중화 ADC의 신호 처리 및 시스템 측면

- 단순 램프 ADC의 MATLAB Simulink 모델

- “Principles of Data Acquisition and Conversion” (PDF). 《ti.com》. 텍사스 인스트루먼트. April 2015. 2024년 10월 29일에 확인함.