패스 트랜지스터 로직

전자공학에서 패스 트랜지스터 로직(Pass transistor logic, PTL)은 집적 회로 설계에 사용되는 여러 논리 제품군을 설명하는 데 사용된다. 패스 트랜지스터 로직은 중복된 트랜지스터를 제거하여 다양한 논리 게이트를 만드는 데 사용되는 트랜지스터 수를 줄인다. 트랜지스터는 전원 전압에 직접 연결된 스위치가 아니라 회로의 노드 간에 논리 레벨을 전달하는 스위치로 사용된다.[1] 이렇게 하면 활성 장치 수가 줄어들지만 각 단계에서 높음 및 낮음 논리 레벨 간의 전압 차이가 줄어드는 단점이 있다(패스 트랜지스터는 약간의 저항이 있고 레벨 복원을 제공하지 않기 때문). 직렬로 연결된 각 트랜지스터는 입력보다 출력에서 포화도가 낮다.[2] 여러 장치가 논리 경로에서 직렬로 연결된 경우 신호 전압을 전체 값으로 복원하기 위해 기존에 제작된 게이트가 필요할 수 있다. 이와 대조적으로 기존 CMOS 논리는 트랜지스터를 스위치하여 출력이 전원 공급 장치 레일 중 하나에 연결되도록 하므로(개방 컬렉터 방식을 연상시킴) 순차 체인의 논리 전압 레벨이 감소하지 않는다. 적절한 성능을 보장하기 위해 회로 시뮬레이션이 필요할 수 있다.

응용

[편집]

패스 트랜지스터 로직은 동일한 기능이 완전 보완 CMOS 논리로 구현된 것보다 트랜지스터 수가 적고, 더 빠르게 실행되며, 전력 소모가 적은 경우가 많다.[3]

XOR은 최악의 경우 카노 맵을 가지며, 간단한 게이트로 구현하면 다른 어떤 기능보다 더 많은 트랜지스터를 필요로 한다. 트랜지스터가 더 비쌌던 시절, Z80 및 기타 여러 칩의 설계자는 간단한 게이트 대신 패스 트랜지스터 로직을 사용하여 XOR을 구현함으로써 몇 개의 트랜지스터를 절약하려는 동기를 부여받았다.[4]

패스 트랜지스터 회로의 기본 원리

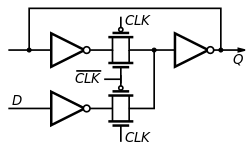

[편집]MOSFET 패스 트랜지스터는 게이트의 전압 신호(예: SRAM 셀 또는 게이티드 D 래치의 클럭 신호)에 따라 드레인과 소스 사이의 경로를 켜거나 끄는 전자 스위치이다.

패스 트랜지스터는 레벨 복원을 제공하지 않으며 전도 경로에 작은 비제로 저항이 있기 때문에 다음 논리 단계의 입력 커패시턴스(다음 단계의 게이트 커패시턴스 외에 기생 커패시턴스 포함)를 유효한 논리-높음 또는 논리-낮음 전압 레벨로 충전하는 RC 지연이 증가한다.

적절한 성능을 보장하기 위해 회로 시뮬레이션이 필요할 수 있다.

보완 패스 트랜지스터 로직

[편집]일부 저자는 "보완 패스 트랜지스터 로직"라는 용어를 NMOS 및 PMOS 패스 트랜지스터로 구성된 트랜스미션 게이트를 사용하는 논리 게이트 구현 스타일을 나타내는 데 사용한다.[5]

다른 저자는 "보완 패스 트랜지스터 로직"(CPL)이라는 용어를 NMOS 전용 패스 트랜지스터 네트워크와 그 뒤에 CMOS 출력 인버터로 구성된 논리 게이트 구현 스타일을 나타내는 데 사용한다.[6][7][8]

다른 저자는 "보완 패스 트랜지스터 로직"(CPL)이라는 용어를 듀얼 레일 인코딩을 사용하는 논리 게이트 구현 스타일을 나타내는 데 사용한다. 모든 CPL 게이트에는 두 개의 출력 와이어가 있으며, 둘 다 양의 신호와 보완 신호가 포함되어 있어 인버터가 필요 없다.[9][10][11]

보완 패스 트랜지스터 로직 또는 "차동 패스 트랜지스터 로직"는 특정 장점을 위해 설계된 논리 제품군을 의미한다. 이 논리 제품군을 멀티플렉서 및 래치에 사용하는 것이 일반적이다.

CPL은 직렬 트랜지스터를 사용하여 논리의 가능한 반전 출력 값 사이에서 선택하며, 그 출력은 인버터를 구동한다. CMOS 트랜스미션 게이트는 병렬로 연결된 nMOS 및 pMOS 트랜지스터로 구성된다.

다른 형태

[편집]정적 및 동적 유형의 패스 트랜지스터 로직이 존재하며, 속도, 전력 및 저전압 작동에 대해 서로 다른 특성을 가진다.[12] 집적 회로 전원 전압이 감소함에 따라 패스 트랜지스터 로직의 단점이 더욱 중요해진다. 트랜지스터의 문턱 전압이 전원 전압에 비해 커져 순차 단계 수가 크게 제한된다. 보완 입력이 패스 트랜지스터를 제어하기 위해 종종 필요하기 때문에 추가적인 논리 단계가 필요하다.

각주

[편집]- ↑ Segura, Jaume; Hawkins, Charles F. (2004). 《CMOS electronics: how it works, how it fails》. Wiley-IEEE. 132쪽. ISBN 0-471-47669-2.

- ↑ Maxfield, Clive (2008). 《Bebop to the boolean boogie: an unconventional guide to electronics》. Newnes. 423–6쪽. ISBN 978-1-85617-507-4.

- ↑ Norimitsu Sako. "Patent US7171636: Pass-transistor logic circuit and a method of designing thereof". 'It is known in the art to employ a "pass-transistor logic circuit" to reduce a number of elements and power consumption, and to improve operating speed.'

- ↑ Shirriff, Ken (2013). “Reverse-engineering the Z-80: the silicon for two interesting gates explained”.

- ↑ Yeap, Gary K. (2012) [1998]. 《Practical Low Power Digital VLSI Design》. Springer. 197쪽. ISBN 978-1-4615-6065-4.

- ↑ Oklobdzija, Vojin G. (2017년 12월 19일). 《Digital Design and Fabrication》. CRC Press. 2–39쪽. ISBN 9780849386046.

- ↑ Yano, Kuniaki; Yamanaka, Toshiaki Yamanaka; Nishida, Takeshi; Saito, Mitsuo; Shimohigashi, Katsuhiro; Shimizu, Atsushi (1990). 《A 3.8-ns CMOS 16x16-b multiplier using complementary pass-transistor logic》. 《IEEE Journal of Solid-State Circuits》 25. 388–395쪽. Bibcode:1990IJSSC..25..388Y. doi:10.1109/4.52161.

- ↑ Reynders, Nele; Dehaene, Wim (2015). 《Ultra-Low-Voltage Design of Energy-Efficient Digital Circuits》. Analog Circuits And Signal Processing (ACSP). Springer Switzerland. doi:10.1007/978-3-319-16136-5. ISBN 978-3-319-16135-8. ISSN 1872-082X. LCCN 2015935431.

- ↑ Chen, Wai-Kai, 편집. (2003). 《Logic Design》. CRC Press. 15–7쪽. ISBN 978-0-203-01015-0. OCLC 1029500642.

- ↑ Oklobdzija, Vojin G., 편집. (2001). 《The Computer Engineering Handbook》. Taylor & Francis. 2–23–2–24쪽. ISBN 978-0-8493-0885-7.

- ↑ Pal, Ajit (2014). 〈5.2.3 Pass-Transistor Logic Families〉. 《Low-Power VLSI Circuits and Systems》. Springer. 109–110쪽. ISBN 978-81-322-1937-8.

- ↑ Leondes, Cornelius T. (1995). 《Digital signal processing systems: implementation techniques》. Elsevier. 2쪽. ISBN 0-12-012768-7.

추가 자료

[편집]- Weste; Harris (2005). 《CMOS VLSI Design》 3판. Pearson/Addison-Wesley. ISBN 0-321-14901-7.

- Pucknell, Douglas A.; Eshraghian, Kamran (1994). 《Basic VLSI Design》 3판. Prentice-Hall Of India Pvt. Limited. ISBN 978-81-203-0986-9.